2-116

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

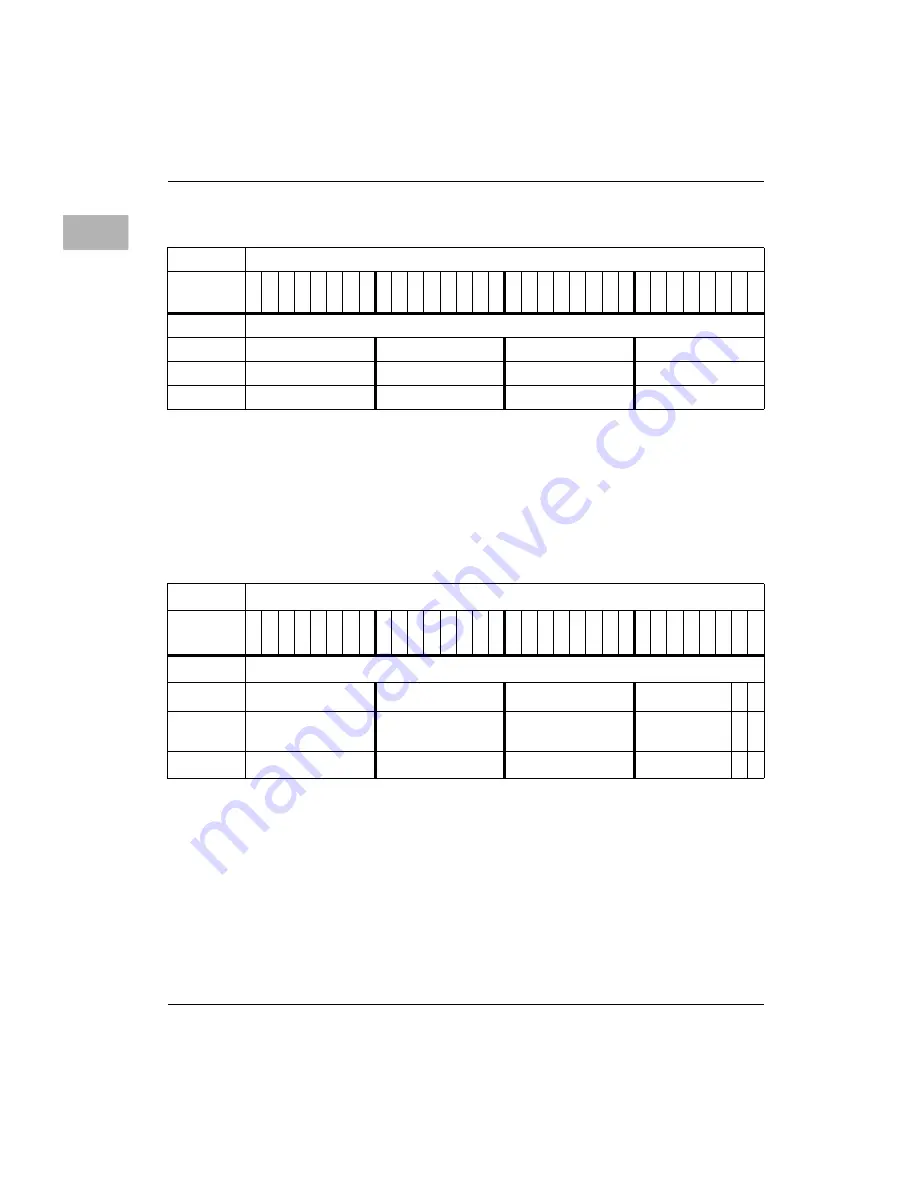

Vendor Identification Register

There are two fields in the Vendor Identification Register which are not

defined for the MPIC implementation but are defined in the MPIC

specification. They are the vendor identification and device ID fields.

STP

STEPPING.The stepping or silicon revision number of

Hawk’s MPIC.

Processor Init Register

P1

PROCESSOR 1. Writing a 1 to P1 will assert the Soft

Reset input of processor 1. Writing a 0 to it will negate the

SRESET signal.

P0

PROCESSOR 0. Writing a 1 to P0 will assert the Soft

Reset input of processor 0. Writing a 0 to it will negate the

SRESET signal.

The Soft Reset input to the 604 is negative edge-sensitive.

Offset

$01080

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

VENDOR IDENTIFICATION

STP

Operation

R

R

R

R

Reset

$00

$00

$00

$00

Offset

$01090

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

PROCESSOR INIT

P1

P0

Operation

R

R

R

R

R/

W

R/

W

Reset

$00

$00

$00

$00

0

0

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...