Functional Description

http://www.motorola.com/computer/literature

2-9

2

Notes

1. Read ahead mode should not be used when data coherency may be

a problem, as there is no way to snoop all MPC bus transactions and

invalidate the contents of the FIFO.

2. Accesses near the top of local memory with read-ahead mode

enabled could cause the MPC master to perform reads beyond the

top of local memory which could result in an MPC bus timeout

error.

The MPC bus transfer types generated by the MPC master depend on the

PCI command code and the INV/GBL bits in the PSATTx registers. The

GBL bit determines whether or not the GBL* signal is asserted for all

portions of a transaction, and is fully independent of the PCI command

code and INV bit.

shows the relationship between PCI command

codes and the INV bit.

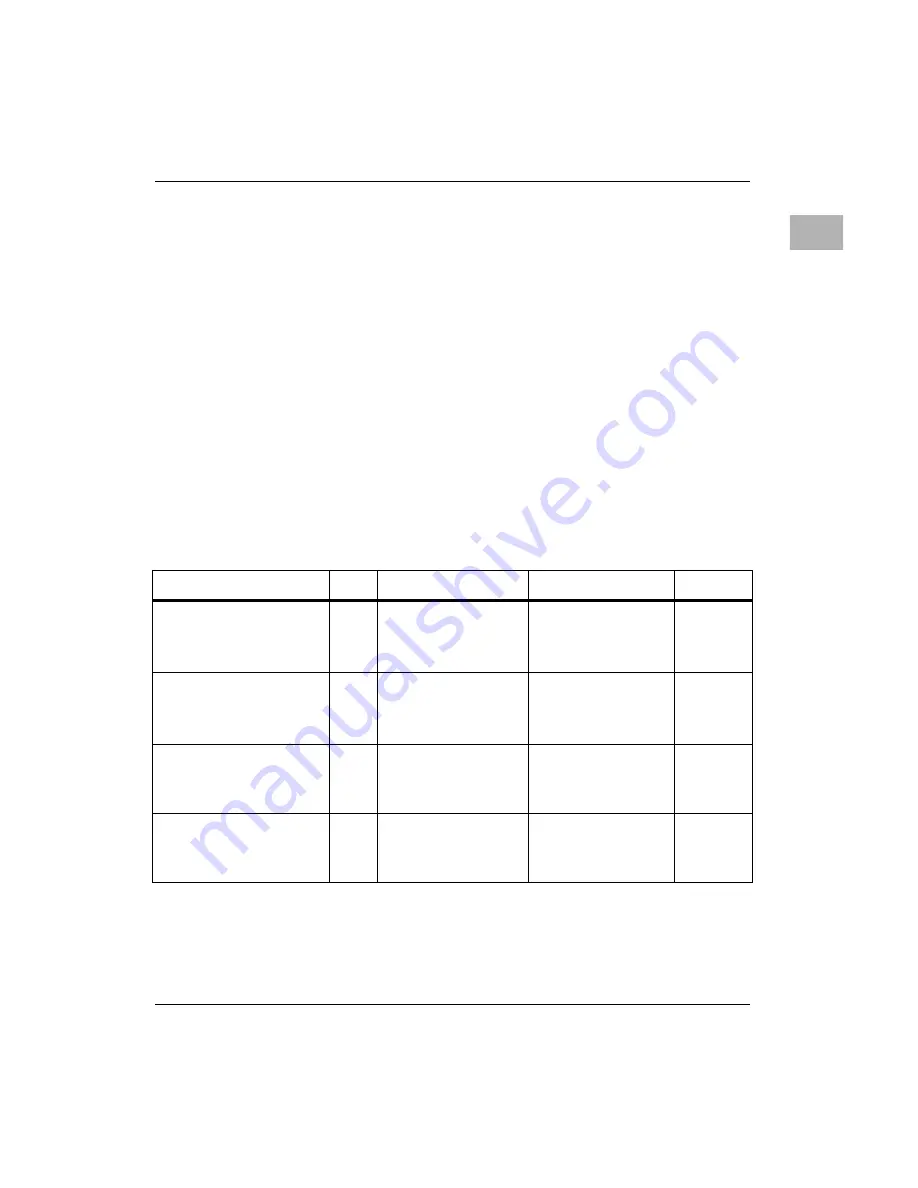

Table 2-2. MPC Transfer Types

The MPC master incorporates an optional operating mode called Bus Hog.

When Bus Hog is enabled, the MPC master will continually request the

MPC bus for the entire duration of each PCI transfer. When Bus Hog is not

PCI Command Code

INV

MPC Transfer Type

MPC Transfer Size

TT0-TT4

Memory Read

Memory Read Multiple

Memory Read Line

0

Read

Burst/Single Beat

01010

Memory Read

Memory Read Multiple

Memory Read Line

1

Read With Intent to

Modify

Burst/Single Beat

01110

Memory Write

Memory Write and

Invalidate

x

Write with Kill

Burst

00110

Memory Write

Memory Write and

Invalidate

x

Write with Flush

Single Beat

00010