Chapter 2 Programming Details

MVME3100 Programmer’s Guide (V3100A/PG1)

27

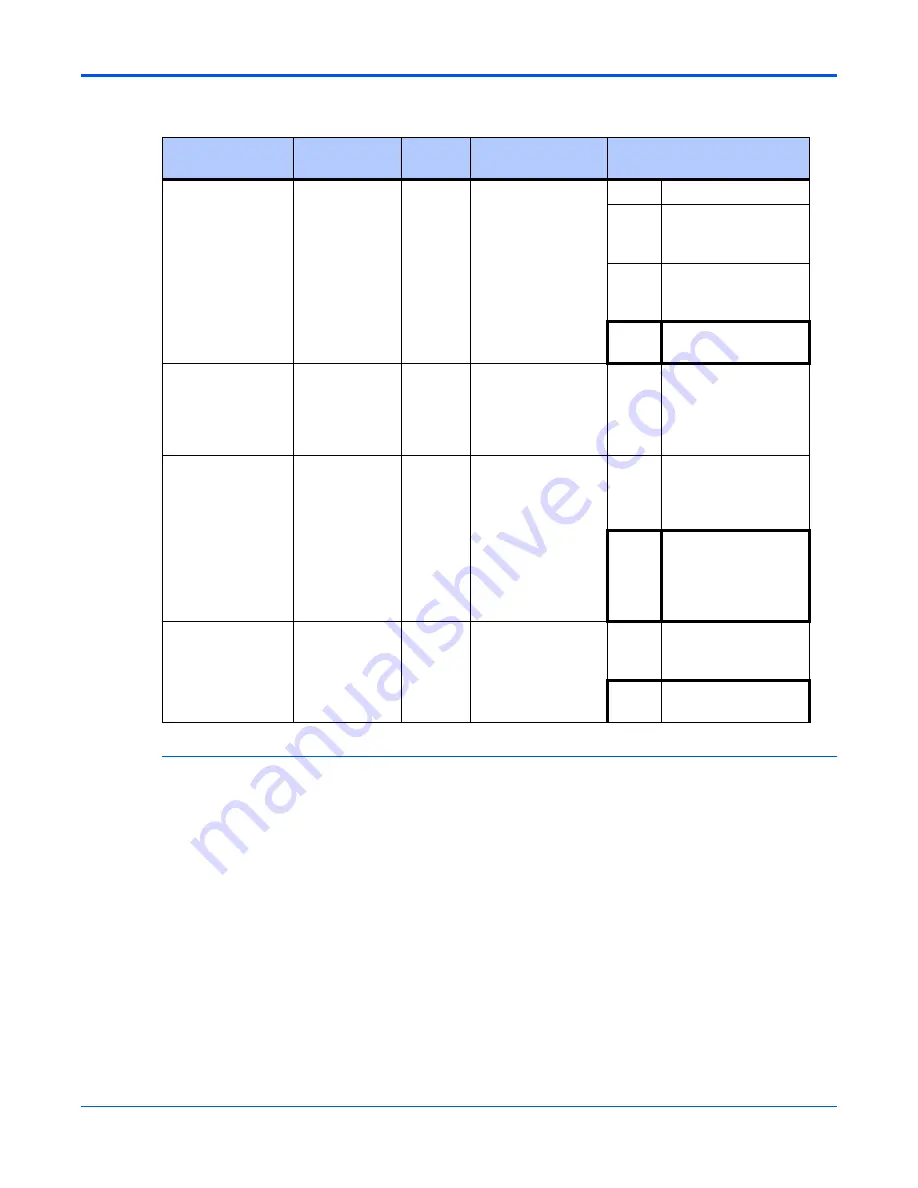

Notes

1.

The selected configuration settings are indicated by dark cell outlines.

2.

External arbitration is required.

3.

e500 core does not boot until configured by an external master.

4.

Dependent on PCI/PCI-X mode configuration.

5.

Required to meet 2 ns hold time requirement.

6.

Meets 0.7 ns hold time requirement.

7.

Local bus LAD[0:31] is sampled during POR, but only LAD[28:31] are configurable by resistor

option. Software can use this value to inform the firmware or operating system about initial board

configuration.

LGPL3, LGPL5

Fixed

11

Boot Sequencer

Configuration

00

Reserved

01

Boot sequencer

enabled with normal

I2C address mode

10

Boot sequencer

enabled with extended

I2C address mode

11

Boot sequencer

disabled

LAD [28:31]

Resistor

7

XX

General-Purpose

POR Configuration

XX

General-purpose POR

configuration vector to

be placed in

CPPORCR register

bits

MSRCID0

Resistor

1

Memory Debug

Configuration

0

Debug info from the

LBC is driven on

MSRCID & MDVAL

pins

1

Debug info from the

DDR SDRAM

controller is driven on

MSRCID & MDVAL

pins

MSRCID1

Resistor

1

DDR Debug

Configuration

0

Debug info on ECC

pins instead of normal

ECC

8

1

ECC pins function in

normal mode

Table 2-1. MPC8540 Power-on Reset Configuration Settings (continued)

MPC8540 Signal

Select Option

Default

Setting

Description

State of Bit vs Function

1