1-18

MPC8240 Integrated Processor User’s Manual

Power Management

1.5 Power Management

TheMPC8240 provides both automatic and program-controllable power reduction modes

for progressive reduction of power consumption.

The MPC8240 has independent power management functionality for both the processor

core and the peripheral logic.The MPC8240 provides hardware support for three levels of

programmable power reduction for both the processor and the peripheral logic. Doze, nap,

and sleep modes are invoked by register programming—HID0 in the case of the processor

core and configuration registers in the case of the peripheral logic block.

The processor and peripheral logic blocks are both fully static, allowing internal logic states

to be preserved during all power-saving modes. The following sections describe the

programmable power modes.

1.5.1 Programmable Processor Power Management Modes

Table 1-1 summarizes the programmable power-saving modes for the processor core.

These are very similar to those available in the MPC603e device.

1.5.2 Programmable Peripheral Logic Power Management

Modes

The following subsections describe the power management modes of the peripheral logic.

Table 1-2 summarizes the programmable power-saving modes for the peripheral logic

block.

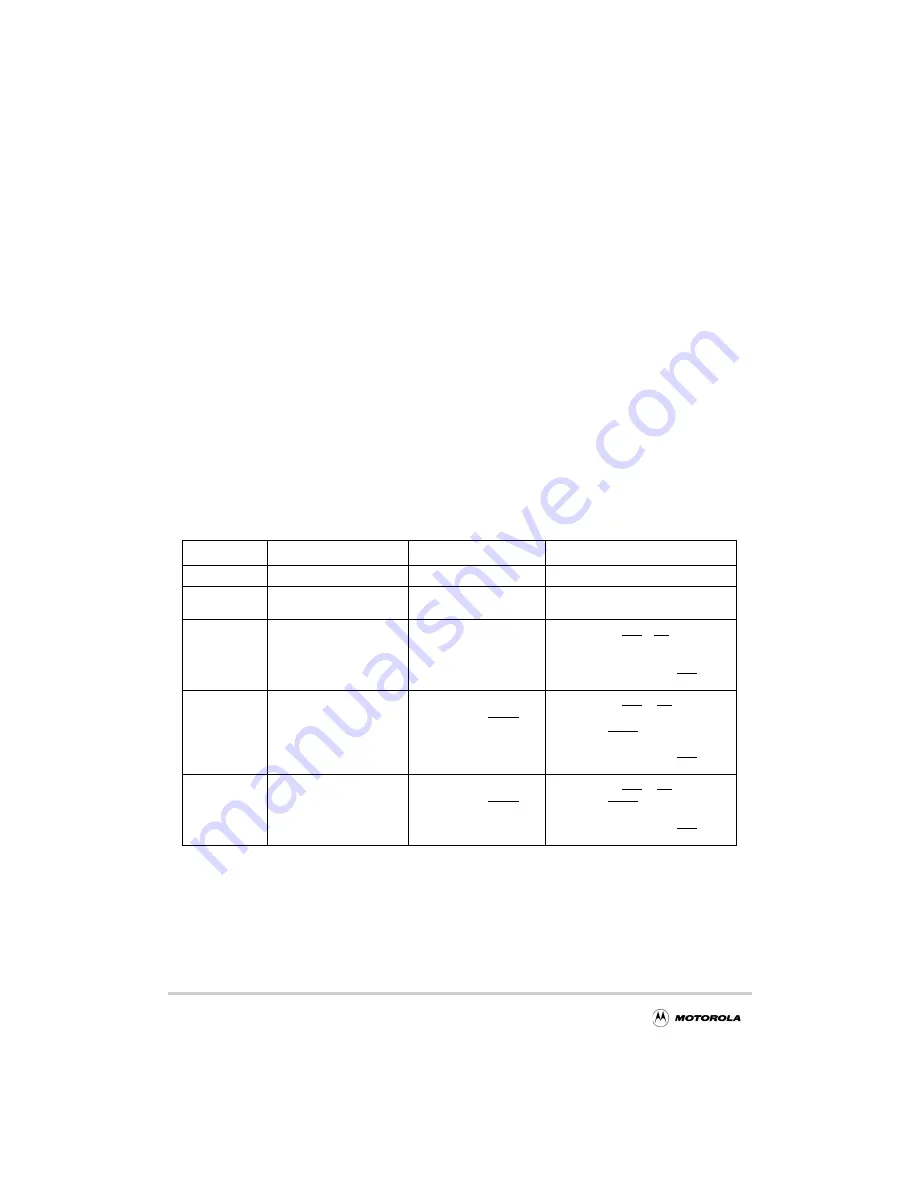

Table 1-1. Programmable Processor Power Modes

PM Mode

Functioning Units

Activation Method

Full-Power Wake Up Method

Full power

All units active

—

—

Full power

(with DPM)

Requested logic by

demand

By instruction dispatch

—

Doze

Bus snooping

Data cache as needed

Decrementer timer

Controlled by software

(write to HID0)

External asynchronous exceptions

(assertion of SMI or int),

Decrementer exception

Hard or soft reset

Machine check exception (mcp)

Nap

Decrementer timer

Controlled by software

(write to HID0) and

qualified with QACK

from peripheral logic

External asynchronous exceptions

(assertion of SMI, or int)

Decrementer exception

Negation of QACK by peripheral logic

Hard or soft reset

Machine check exception (mcp)

Sleep

None

Controlled by software

(write to HID0) and

qualified with QACK

from peripheral logic

External asynchronous exceptions

(assertion of SMI, or int)

Negation of QACK by peripheral logic

Hard or soft reset

Machine check exception (mcp)

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...