E-22

MPC8240 Integrated Processor User’s Manual

Implementation-Specific Registers from 603e

E.2.3 Primary and Secondary Hash Address Registers

(HASH1 and HASH2)

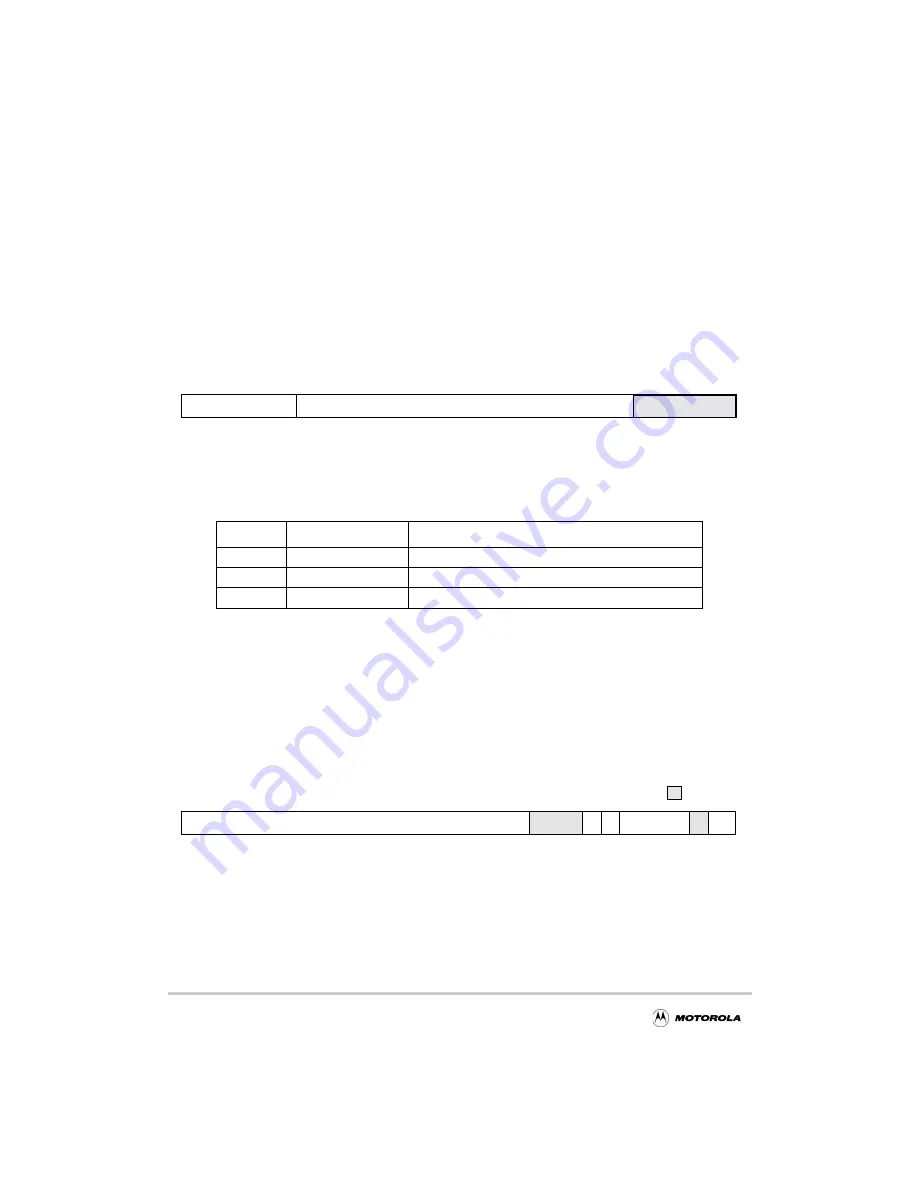

The HASH1 and HASH2 registers contain the physical addresses of the primary and

secondary PTEGs for the access that caused the TLB miss exception. For convenience, the

603e automatically constructs the full physical address by routing bits 0–6 of SDR1 into

HASH1 and HASH2 and clearing the lower 6 bits. These registers are read-only and are

constructed from the contents of the DMISS or IMISS register (the register choice is

determined by which miss was last acknowledged). The format for the HASH1 and HASH2

registers is shown in Figure E-24.

Figure E-24. HASH1 and HASH2 Registers

Table E-17 describes the bit settings of the HASH1 and HASH2 registers.

E.2.4 Required Physical Address Register (RPA)

The RPA register is shown in Figure E-25. During a page table search operation, the

software must load the RPA with the second word of the correct PTE. When the tlbld or

tlbli instruction is executed, the contents of the RPA register and the DMISS or IMISS

register are merged and loaded into the selected TLB entry. The referenced (R) bit is

ignored when the write occurs (no location exists in the TLB entry for this bit). The RPA

register can be read and written by software.

Figure E-25. Required Physical Address Register (RPA)

Table E-17. HASH1 and HASH2 Bit Settings

Bits

Name Description

0–6

HTABORG[0–6]

Copy of the upper 7 bits of the HTABORG field from SDR1

7–25

Hashed page address

Address bits 7–25 of the PTEG to be searched

26–31

—

Reserved

0

6

7

25

26

31

HTABORG[0–6]

Hashed Page Address

0 0 0 0 0 0

0

19 20

22

23 24 25

28 29 30 31

Reserved

RPN

R

C

WIMG

PP

0 0 0

0

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...