E-8

MPC8240 Integrated Processor User’s Manual

PowerPC Register Set

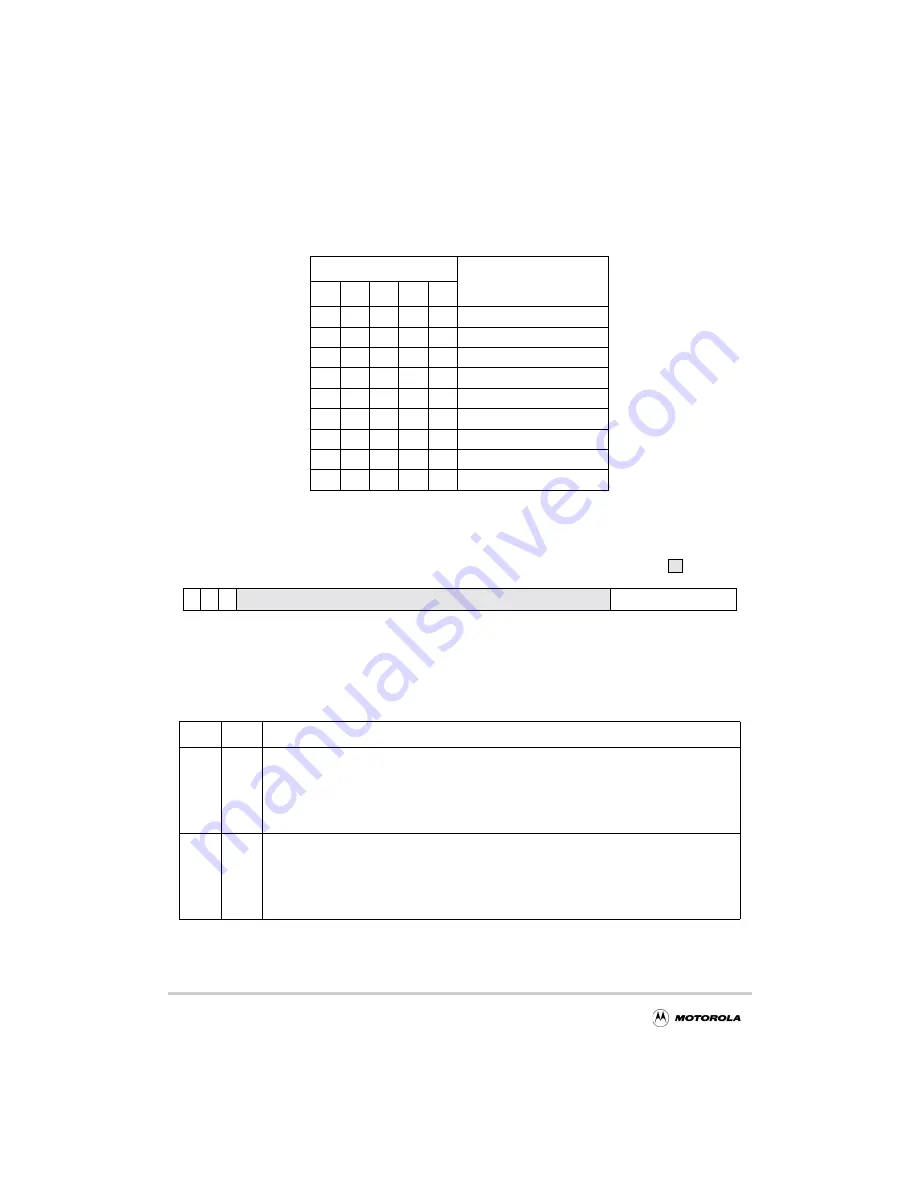

Table E-5 illustrates the floating-point result flags used by PowerPC processors. The result

flags correspond to FPSCR bits 15–19.

E.1.1.5 XER Register (XER)

The XER register (XER) is a 32-bit, user-level register shown in Figure E-6.

.

Figure E-6. XER Register

The bit definitions for XER are shown in Table E-6.

Table E-5. Floating-Point Result Flags in FPSCR

Result Flags (Bits 15–19)

Result Value Class

C

<

>

=

?

1

0

0

0

1

Quiet NaN

0

1

0

0

1

–Infinity

0

1

0

0

0

–Normalized number

1

1

0

0

0

–Denormalized number

1

0

0

1

0

–Zero

0

0

0

1

0

+Zero

1

0

1

0

0

+Denormalized number

0

0

1

0

0

+Normalized number

0

0

1

0

1

+Infinity

Table E-6. XER Bit Definitions

Bit(s)

Name

Description

0

SO

Summary overflow. The summary overflow bit (SO) is set whenever an instruction (except mtspr)

sets the overflow bit (OV). Once set, the SO bit remains set until it is cleared by an mtspr

instruction (specifying the XER) or an mcrxr instruction. It is not altered by compare instructions,

nor by other instructions (except mtspr to the XER, and mcrxr) that cannot overflow. Executing an

mtspr instruction to the XER, supplying the values zero for SO and one for OV, causes SO to be

cleared and OV to be set.

1

OV

Overflow. The overflow bit (OV) is set to indicate that an overflow has occurred during execution of

an instruction. Add, subtract from, and negate instructions having OE = 1 set the OV bit if the carry

out of the msb is not equal to the carry out of the msb + 1, and clear it otherwise. Multiply low and

divide instructions having OE = 1 set the OV bit if the result cannot be represented in 64 bits

(mulld, divd, divdu) or in 32 bits (mullw, divw, divwu), and clear it otherwise. The OV bit is not

altered by compare instructions that cannot overflow (except mtspr to the XER, and mcrxr).

Reserved

SO OV CA

0 0000 0000 0000 0000 0000 0

Byte count

0

1

2

3

24 25

31

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...