Chapter 13. Error Handling

13-7

Error Reporting

13.3.1.2 Flash Write Error

The MPC8240 allows processor writes to the local ROM space when

PICR1[FLASH_WR_EN] is set and PICR2[FLASH_WR_LOCKOUT] is cleared.

Otherwise, any processor write transaction to the local ROM space results in a Flash write

error. Attempts to write to local ROM space from a PCI master or the DMA controller also

cause Flash write errors. When a Flash write error occurs, ErrDR2[0] is set.

The ROM/Flash interface on the MPC8240 accommodates only single-beat, datapath-sized

(8-, 32-, or 64-bit depending on the configuration) writes to Flash memory. This requires

that all writes to system ROM space must be either caching-inhibited, or

caching-allowed/write-through. Any burst write to ROM space causes a Flash write error.

Software must partition larger data into individual datapath-sized (8-, 32-, or 64-bit) write

operations.Note that an attempt to write to Flash with a data size larger than the data path

size (for example, a 32-bit write to 8-bit Flash) does not cause a Flash write error, but the

data in the unused byte lanes is ignored.

13.3.1.3 Processor Write Parity Error

When both ErrEnR2[2] and MCCR2[WRITE_PAR_CHK] are set, the MPC8240 checks

processor parity on memory write cycles with the stipulations described in Table 13-2.

When a processor write parity error occurs, ErrDR2[2] is set. Note that the MPC8240 does

not check parity for write transactions to PCI or the local ROM address space.

13.3.2 Memory Interface Errors

The memory interface of the MPC8240 detects read parity, ECC, memory select, and

refresh overflow errors. The MPC8240 detects parity errors on the data bus during memory

(DRAM/EDO/SDRAM) read cycles. The memory controller can detect single-bit and

multi-bit errors for local memory read transactions. Since the ECC logic corrects single-bit

errors, they are reported only when the number of errors in the ECC single-bit error counter

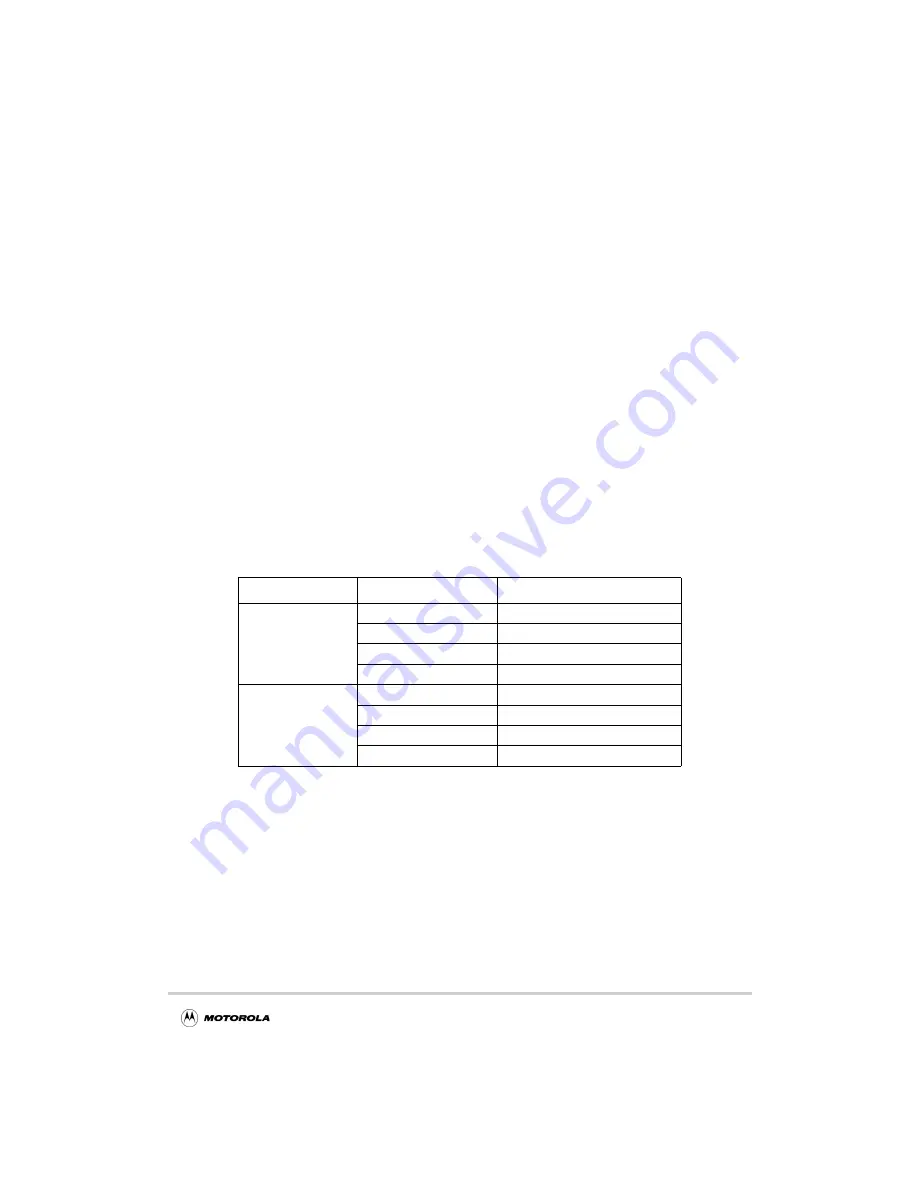

Table 13-2. Processor Write Parity Checking

Memory Type

Memory Error Protocol

1

1

See Table 6-9 or Table 6-20 for specific bit settings.

Processor Write Parity Checking

SDRAM

None

Not supported

Parity

Yes

RMW parity

Not supported

ECC

Yes

FPM/EDO DRAM

None

Not supported

Parity

Yes

RMW parity

Not supported

ECC

Not supported

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...