Chapter 7. PCI Bus Interface

7-31

PCI Error Functions

7.6.1 PCI Parity

Generating parity is not optional; it must be performed by all PCI-compliant devices. All

PCI transactions, regardless of type, calculate even parity; that is, the number of 1s on the

AD[31:0], C/BE[3:0], and PAR signals all sum to an even number.

Parity provides a way to determine, on each transaction, if the initiator successfully

addressed the target and transferred valid data. The C/BE[3:0] signals are included in the

parity calculation to ensure that the correct bus command is performed (during the address

phase) and correct data is transferred (during the data phase). The agent responsible for

driving the bus must also drive even parity on the PAR signal one clock cycle after a valid

address phase or valid data transfer, as shown in Figure 7-11.

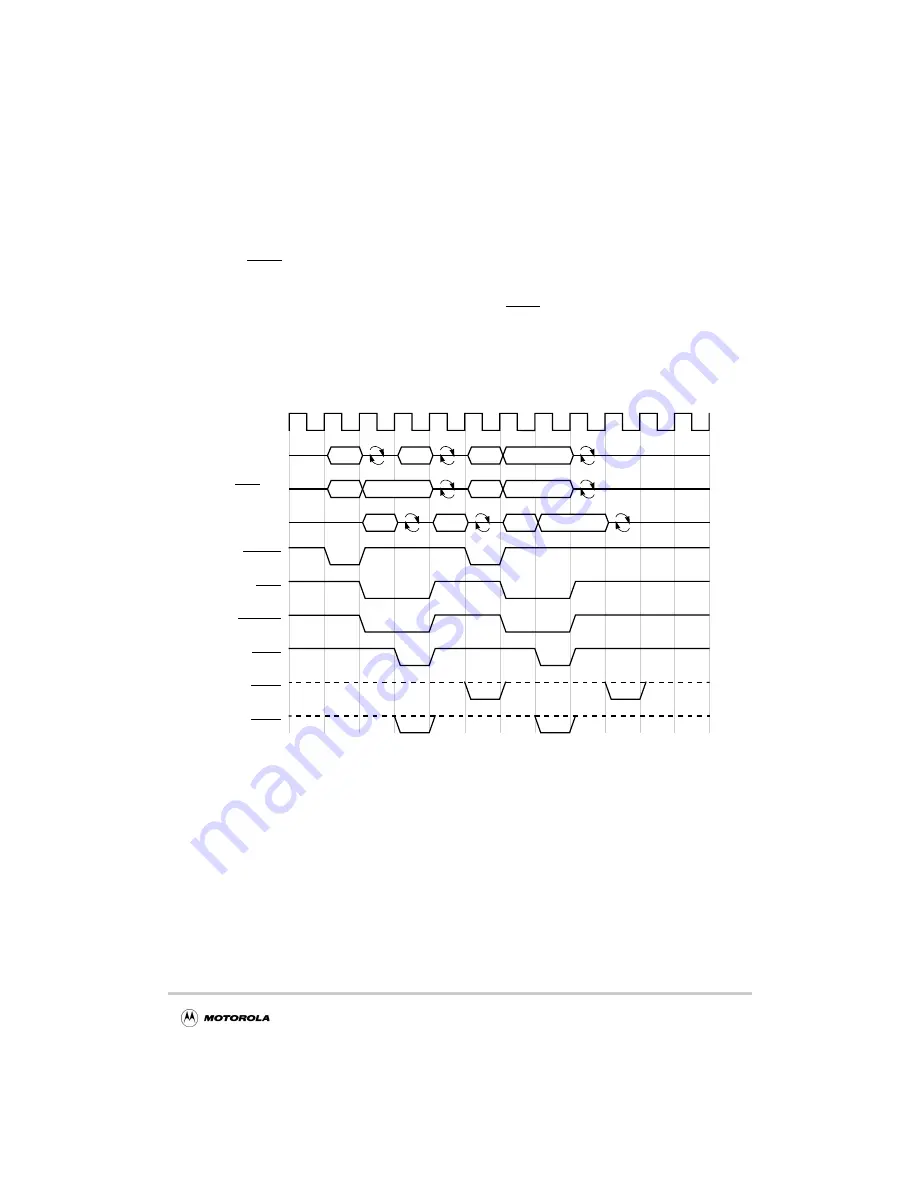

Figure 7-11. PCI Parity Operation

During the address and data phases, parity covers all 32 address/data signals and the four

command/byte enable signals regardless of whether all lines carry meaningful information.

Byte lanes not actually transferring data must contain stable (albeit meaningless) data and

are included in parity calculation. During configuration, special-cycle, or

interrupt-acknowledge commands, some address lines are not defined but are driven to

stable values and are included in parity calculation.

Agents that support parity checking must set the detected parity error bit in the PCI status

register when a parity error is detected. Any additional response to a parity error is

controlled by the parity error response bit in the PCI command register. If the parity error

response bit is cleared, the agent ignores all parity errors.

PCI_SYNC_IN

PAR

FRAME

AD[0:31]

ADDR

IRDY

DEVSEL

C/BE[0:3]

DATA

Byte enables

Byte enables

TRDY

PERR

SERR

CMD

DATA

ADDR

CMD

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...