IGLOO2 FPGA Adaptive FIR Filter Demo

12

Revision 2

CoreUART

The CoreUART IP is used to transfer the data between the Host PC (GUI) and the IGLOO2 device. The

CoreUART Configuration is as follows:

•

Version: 5.2.2

•

TxFIFO: Disable

•

RxFIFO: Disable

•

RxLegacyMode: Disable

•

Baud rate: 115200

•

Number of bits: 8

•

Stop bits: 1

•

Parity: None

Setting Up the Demo Design

The following steps describe how to setup the hardware demo:

1. Connect the jumpers on the IGLOO2 Evaluation Kit board as shown in

Table 3

.

CAUTION:

While making the jumper connections, the power supply switch

SW7

must be

switched off.

2. Connect the Power supply to the J6 connector, switch on the power supply switch,

SW7

.

3. Connect the FlashPro4 programmer to the J5 connector of the IGLOO2 Evaluation Kit board.

4. Connect the Host PC USB port to the J18 USB connector on the IGLOO2 Evaluation Kit board

using the USB mini-B cable.

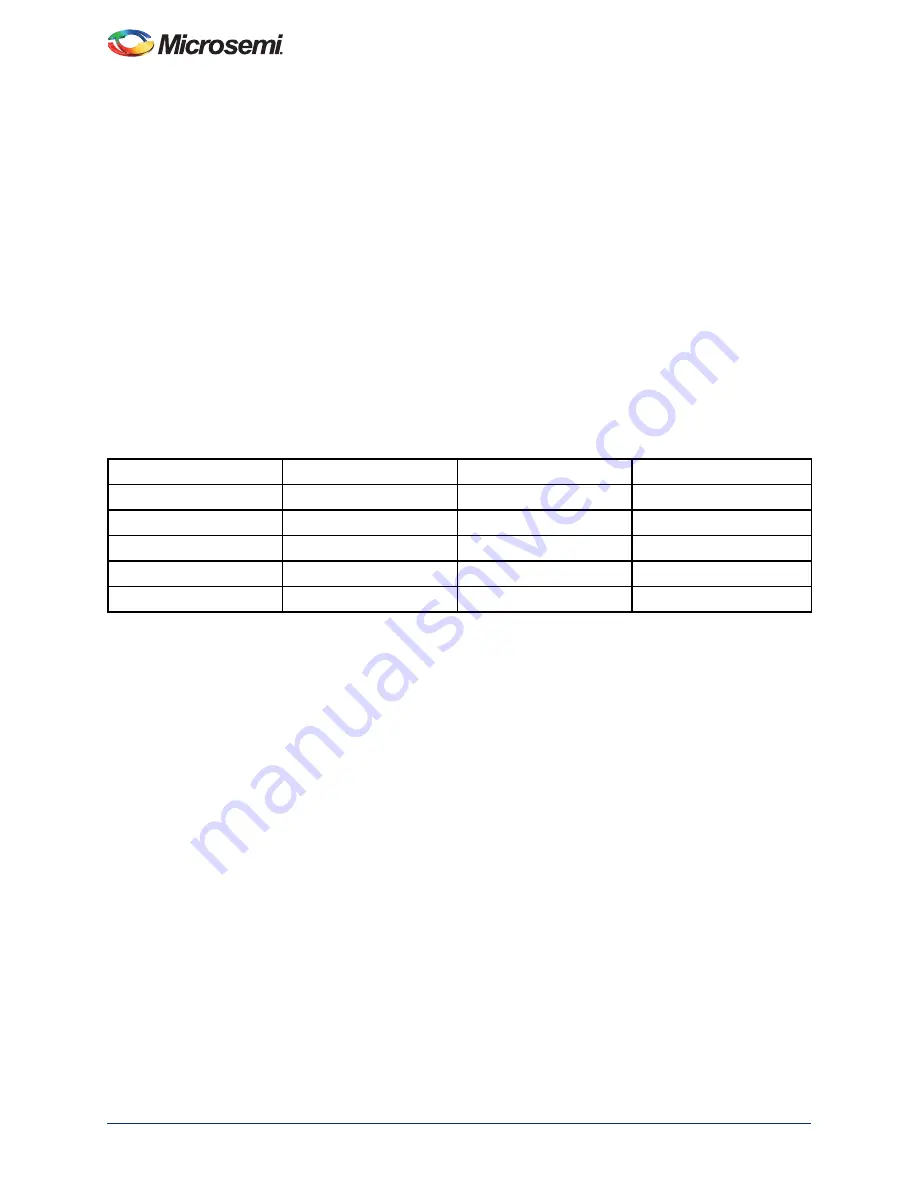

Table 3 •

IGLOO2 FPGA Evaluation Kit Jumper Settings

Jumper

Pin (From)

Pin (To)

Comments

J22

1

2

Default

J23

1

2

Default

J24

1

2

Default

J8

1

2

Default

J3

1

2

Default

Superseded