PolarFire FPGA 1G Ethernet Loopback Using IOD CDR

Microsemi Proprietary DG0799 Demo Guide Revision 3.0

5

2.3.2

Design Implementation

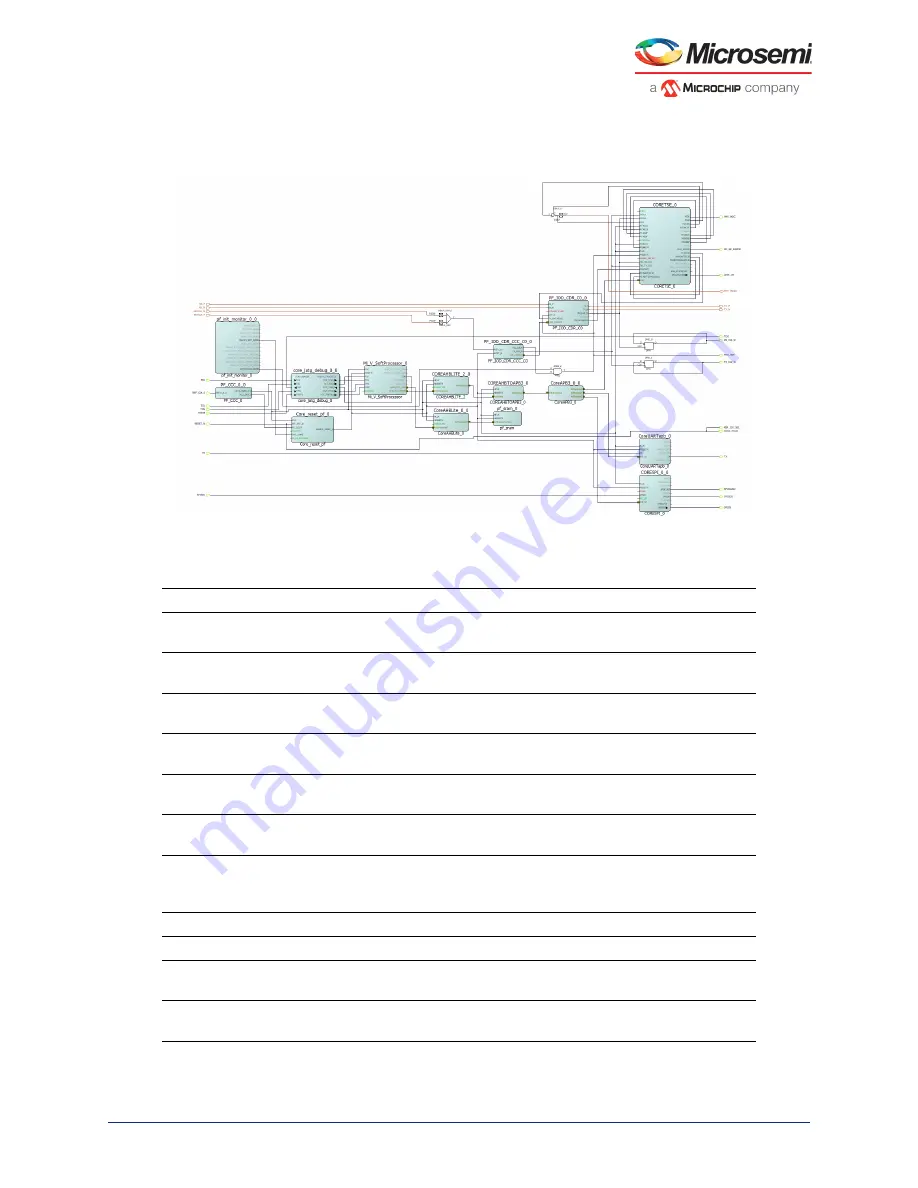

page 5 shows the top-level Libero implementation of the demo design.

Figure 2 •

Top-Level Libero Implementation

page 5 lists the important I/O signals of the design.

Table 2 •

I/O Signals

Signal

Direction

Description

RX_P, RX_N

Input

IOD CDR receive signals connected to the VSC PHY transmit

data signals.

TX_P, TX_N

Output

IOD CDR transmit signals connected to the VSC PHY receive

data signals.

REFCLK_N,

REFCLK_P

Input

125 MHz input clock received from the on-board ZL30364 and

fed to NWC_PLL_0.

RESET_N

Input

Active low Mi-V reset. Asserted by pressing the on-board K22

push-button.

REF_CLK_0

Input

50 MHz input clock received from the on-board 50 MHz

oscillator and fed to PF_CCC_0.

TCK, TDI, TMS,

TRSTB

Input

JTAG signals interfaced to the soft processor for debugging.

LINK_OK

Output

Link status indicator. Provides the link

up

or

down

status with

the on-board PHY. This signal is mapped to on-board LED7.

The LED ON condition indicates that the link is up

.

PHY_RST

Output

Active high reset signal to the on-board VSC8575 PHY.

PHY_MDC

Output

Management Data IO clock fed to the on-board VSC8575 PHY.

PHY_MDIO

Output

Management Data IO Interface for accessing the on-board

VSC8575 PHY registers.

coma_mode

Output

Signal held low to keep the VSC PHY fully active when it is out

of reset.