MC80F0104/0204

Preliminary

90

Mar. 2005 Ver 0.2

The reset should not be activated before V

DD

is restored to

its normal operating level, and must be held active long

enough to allow the oscillator to restart and stabilize.

Note:

After STOP instruction, at least two or more NOP instruc-

tion should be written.

Ex)

LDM CKCTLR,#0FH ;more than 20ms

LDM SSCR,#5AH

STOP

NOP ;for stabilization time

NOP ;for stabilization time

In the STOP operation, the dissipation of the power asso-

ciated with the oscillator and the internal hardware is low-

ered; however, the power dissipation associated with the

pin interface (depending on the external circuitry and pro-

gram) is not directly determined by the hardware operation

of the STOP feature. This point should be little current

flows when the input level is stable at the power voltage

level (V

DD

/V

SS

); however, when the input level gets high-

er than the power voltage level (by approximately 0.3 to

0.5V), a current begins to flow. Therefore, if cutting off the

output transistor at an I/O port puts the pin signal into the

high-impedance state, a current flow across the ports input

transistor, requiring to fix the level by pull-up or other

means.

Release the STOP mode

The source for exit from STOP mode is hardware reset, ex-

ternal interrupt, Timer(EC0,1), Watch Timer, WDT, SIO

or UART. Reset re-defines all the Control registers but

does not change the on-chip RAM. External interrupts al-

low both on-chip RAM and Control registers to retain their

values.

If I-flag = 1, the normal interrupt response takes place. If I-

flag = 0, the chip will resume execution starting with the

instruction following the STOP instruction. It will not vec-

tor to interrupt service routine. (refer to Figure 19-4 )

When exit from Stop mode by external interrupt, enough

oscillation stabilizing time is required to normal operation.

Figure 19-5 shows the timing diagram. When released

from the Stop mode, the Basic interval timer is activated on

wake-up. It is increased from 00

H

until FF

H

. The count

overflow is set to start normal operation. Therefore, before

STOP instruction, user must be set its relevant prescaler di-

vide ratio to have long enough time (more than 20msec).

This guarantees that oscillator has started and stabilized.

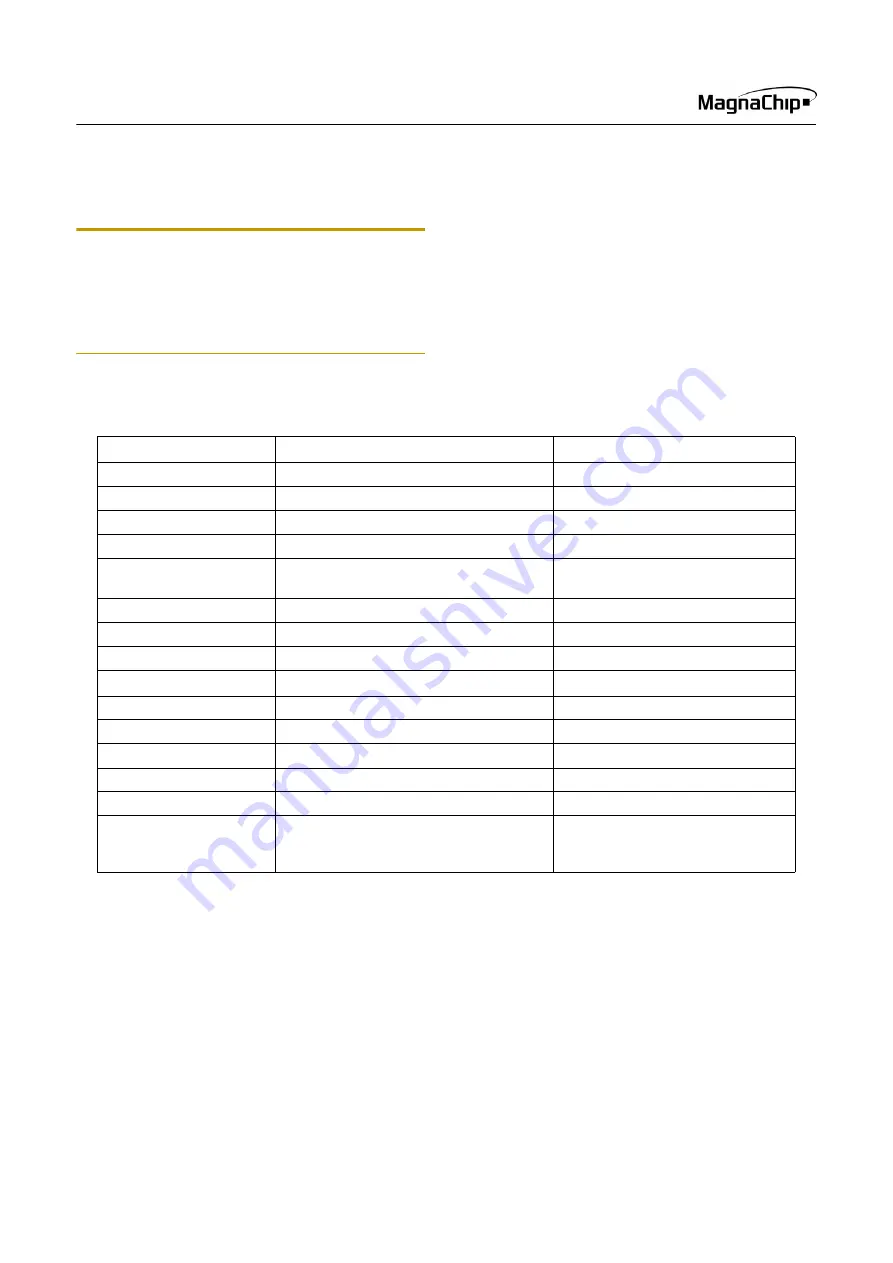

Peripheral

STOP Mode

SLEEP Mode

CPU

Stop

Stop

RAM

Retain

Retain

Basic Interval Timer

Halted

Operates Continuously

Watchdog Timer

Stop (Only operates in RC-WDT mode)

Stop

Timer/Counter

Halted (Only when the event counter mode

is enabled, timer operates normally)

Operates Continuously

Buzzer, ADC

Stop

Stop

SIO

Only operate with external clock

Only operate with external clock

UART

Only operate with external clock

Only operate with external clock

Oscillator

Stop (X

IN

=L, X

OUT

=H)

Oscillation

I/O Ports

Retain

Retain

Control Registers

Retain

Retain

Internal Circuit

Stop mode

Sleep mode

Prescaler

Retain

Active

Address Data Bus

Retain

Retain

Release Source

Reset, Timer(EC0,1), SIO, UART(using

ACLK), Watchdog Timer (RC-WDT mode),

External Interrupt

Reset, All Interrupts

Table 19-1 Peripheral Operation During Power Saving Mode

Содержание MC80F0104

Страница 108: ...MC80F0104 0204 Preliminary 104 Mar 2005 Ver 0 2 25 Emulator EVA Board Setting...

Страница 115: ...APPENDIX...

Страница 116: ......

Страница 124: ...viii Mar 2005 Ver 0 2 MC80F0104 0204 Preliminary...