BRUSHLESS DC MOTOR COMMUTATOR/CONTROLLER

FEATURES:

•

Direct drive of P-Channel and N-Channel FETs (LS7280)

•

Direct drive of PNP and NPN transistors (LS7282)

•

Six outputs drive power switching bridge directly

•

Open or closed loop motor speed control.

•

+5V to +40V operation (V

DD -

V

SS

)

•

Externally selectable input to output code for 60°,

120°, 240°, or 300° electrical sensor spacing.

•

Three-phase or four-phase operation

•

Analog Speed control

•

Direction control

•

Output Enable control

•

Positive Static Braking

•

Overcurrent Sensing

•

LS7280, LS7282 (DIP); LS7280-S, LS7282-S (SOIC);

LS7280-TS, LS7282-TS (TSSOP)

- See Connection Diagram -

DESCRIPTION:

The LS7280/LS7282 are MOS integrated circuits de-

signed to generate the signals necessary to control a

three phase or four phase brushless DC motor. They

are the basic building blocks of a brushless DC motor

controller. The circuits respond to changes at the

SENSE inputs, originating at the motor position sensors,

to provide electronic commutation of the motor wind-

ings. Pulse Width Modulation of outputs for motor speed

control is accomplished through either the ENABLE in-

put or through the Analog input (VTRIP) in conjunction

with the OSCILLATOR input. Overcurrent circuitry is

provided to protect the windings, associated drivers and

power supply. The overcurrent circuitry causes the ex-

ternal output drivers to switch off immediately upon

sensing the overcurrent condition and on again only

when the overcurrent condition disappears and the pos-

itive edge of either the ENABLE input or the sawtooth

OSCILLATOR occurs. This limits the overcurrent sense

cycling to the chopping rate of the ENABLE input or the

sawtooth OSCILLATOR.

A positive braking feature is provided to effect rapid de-

celeration. While the LS7282 is designed for driving

NPN and PNP transistors (See Fig. 2), the LS7280 is

designed to drive both NMOS and PMOS Power FETs

and develops a full 12V drive for both the N-Channel

and P-Channel devices (See Fig. 1) when using a 12V

power supply.

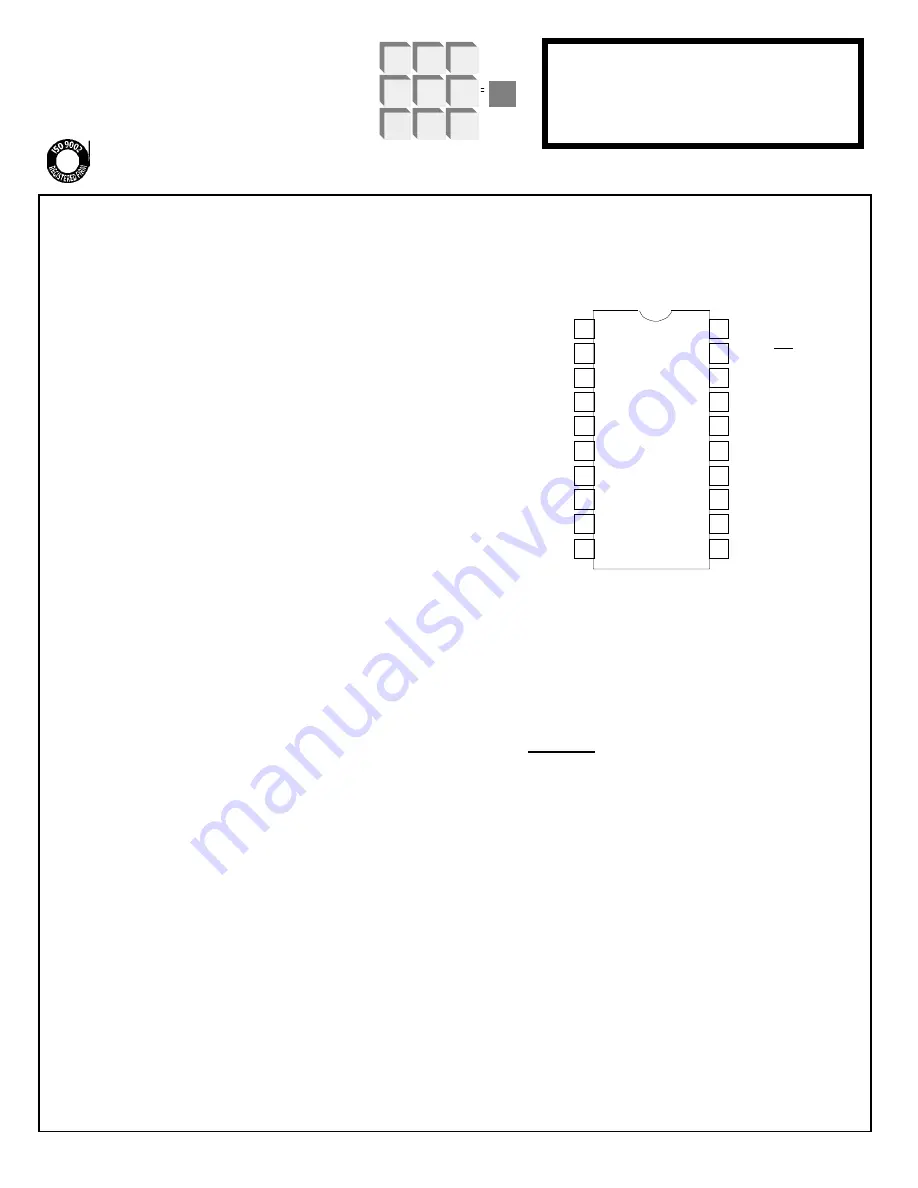

LSI

CS1

OUT 1

OUT 2

OUT 3

OUT 4

COMMON

OUT 5

OUT 6

BRAKE

E N A B L E

CS2

F W D / R E V

V

SS

(-V)

S3

S2

S1

OSCILLATOR

V TRIP

O V E R C U R R E N T S E N S E

V

DD

(+V)

CONNECTION DIAGRAM - TOP VIEW

1

2

3

4

5

6

7

8

9

10

20

11

12

13

14

15

16

17

18

19

INPUT/OUTPUT DESCRIPTION:

COMMUTATION SELECTS (Pins 1, 20)

These inputs are used to select the proper sequence of outputs

based on the electrical separation of the motor position sensors.

See Table 3. Note that in all cases the external output drivers

are disabled for invalid SENSE input codes. Internal pull down

resistors are provided at Pins 1 and 20 causing a logic zero

when these pins are left open.

FORWARD/REVERSE (Pin 19)

This input is used to select the proper sequence of Outputs for

the desired direction of rotation for the Motor (See Table 3). An

internal pull-up resistor holds the input high when left open.

SENSE INPUTS (Pins 15, 16, 17)

These inputs provide control of the output commutation

sequence as shown in Table 3. S1, S2, S3 originate in the posi-

tion sensors of the motor and must sequence in cycle code or-

der. Hall Switch pull-up resistors are provided at Pins 15, 16 and

17. The positive supply of the Hall devices should be common

to the chip V

DD

.

BRAKE (Pin 9)

For the LS7282, a high level at this input unconditionally turns

off Outputs 1, 2 and 3 and turns on Outputs 4, 5 and 6 (See Fig.

2). For the LS7280, a high level at this input turns on Outputs 1,

2 and 3 and Outputs 4, 5 and 6 (See Fig. 1). In both cases,

transistors Q101, Q102 and Q103 cut off and transistors Q104,

Q105 and Q106 turn on, shorting the windings together.

The BRAKE has priority over all other inputs.

7280-011705-1

LSI/CSI

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

LS7280

LS7282

UL

®

A3800

January 2005

- PRELIMINARY -