LTC4260

15

4260fc

For more information

applicaTions inForMaTion

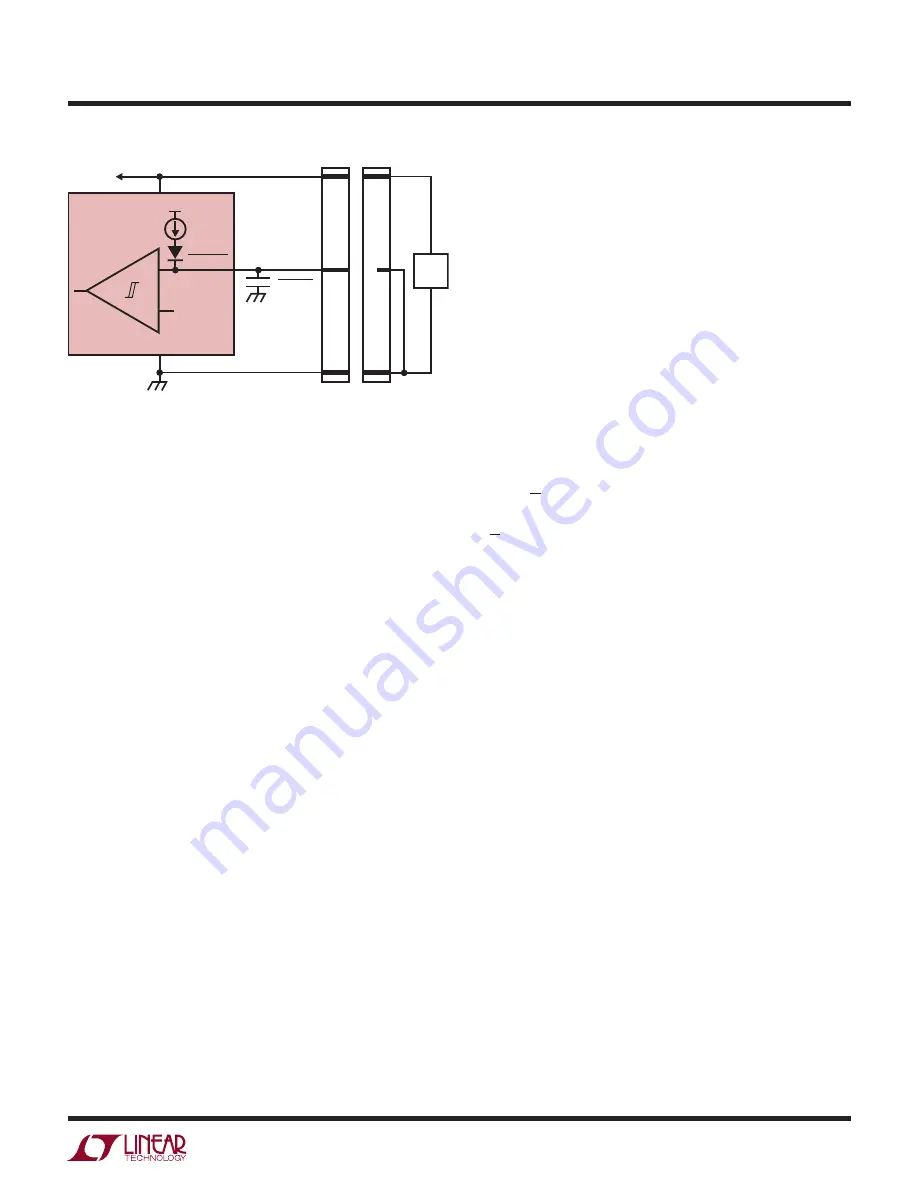

Power Bad Present/Power Bad Fault

When the FB pin drops below its 3.41V threshold the

power bad present bit, C3, goes high. This pulls the GPIO

pin low immediately when configured as PWRGD. If the

FB pin subsequently rises back above the threshold, the

GPIO pin will return to a high impedance state and bit C3

will be cleared.

The power bad fault bit, D3, is set when the GATE-to-

SOURCE voltage is high and the power bad present C3

bit is high. This blanking with the gate voltage prevents

false power bad faults during power-up or power-down.

Fault Alerts

When any of the fault bits in FAULT register D are set,

an optional I

2

C bus alert can be generated by setting the

appropriate bit in the ALERT register B. This allows only

selected faults to generate alerts. At power-up the default

state is to not alert on faults. If an alert is enabled, the cor-

responding fault will cause the

ALERT

pin to pull low. After

the bus master controller broadcasts the Alert Response

Address, the LTC4260 responds with its address on the

SDA line and releases

ALERT

as shown in Figure 11. If

there is a collision between two LTC4260s responding

with their addresses simultaneously, then the device with

the lower address wins arbitration and responds first. The

ALERT

line will also be released if the device is addressed

by the bus master.

–

+

1.235V

GND

MOTHERBOARD

CONNECTOR

PLUG-IN

CARD

SOURCE

OUT

LTC4260

10µA

23

6

BD_PRST 14

C

BD_PRST

LOAD

4260 F04

Figure 4. Plug-In Card Insertion/Removal

Once the

ALERT

signal has been released for one fault,

it will not be pulled low again until the FAULT register

indicates a different fault has occurred or the original

fault is cleared and it occurs again. Note that this means

repeated or continuing faults will not generate alerts until

the associated FAULT register bit has been cleared.

Resetting Faults

Faults are reset with any of the following conditions. First,

a serial bus command writing zeros to the FAULT register

D will clear the associated faults. Second, the entire FAULT

register is cleared when the switch is turned off by either

the ON pin or bit A3 going from high to low, or if the UV

pin is brought below its 1.23V reset threshold, or if INTV

CC

falls below its 3.8V undervoltage lockout threshold. Finally,

when

BDPRST

is brought from high to low, only FAULT

bits D0-D3 and D5 are cleared, the bit D4 that indicates a

BDPRST

change of state will be set. Faults that are still

present (as indicated in the STATUS Register C) cannot

be cleared.

The FAULT register will not be cleared when autoretrying.

When autoretry is disabled the existence of a D0, D1 or D2

fault keeps the switch off. As soon as the fault is cleared,

the switch will turn on. If autoretry is enabled, then a high

value in C0, C1 or C2 will hold the switch off and the FAULT

register is ignored. Subsequently, when the C0, C1 and

C2 bits are cleared, the switch is allowed to turn on again.

Data Converter

The LTC4260 incorporates an 8-bit data converter that

continuously monitors three different voltages. The Δ∑

architecture inherently averages signal noise during the

measurement period. The SOURCE pin uses a 1/40 resis-

tive divider to monitor a full-scale voltage of 102.4V with

0.4V resolution (divider converts 102.4V to 2.56V). The

ADIN pin is monitored with a 2.56V full scale and 10mV

resolution, and the voltage between the V

DD

and SENSE

pins is monitored with a 76.8mV full scale and 300µV

resolution.

The results from each conversion are stored in registers

E, F and G and are updated 10 times per second. Setting

CONTROL register bit A5 invokes a test mode that halts

the data converter updates so that registers E, F and G

can be written to and read from for software testing.