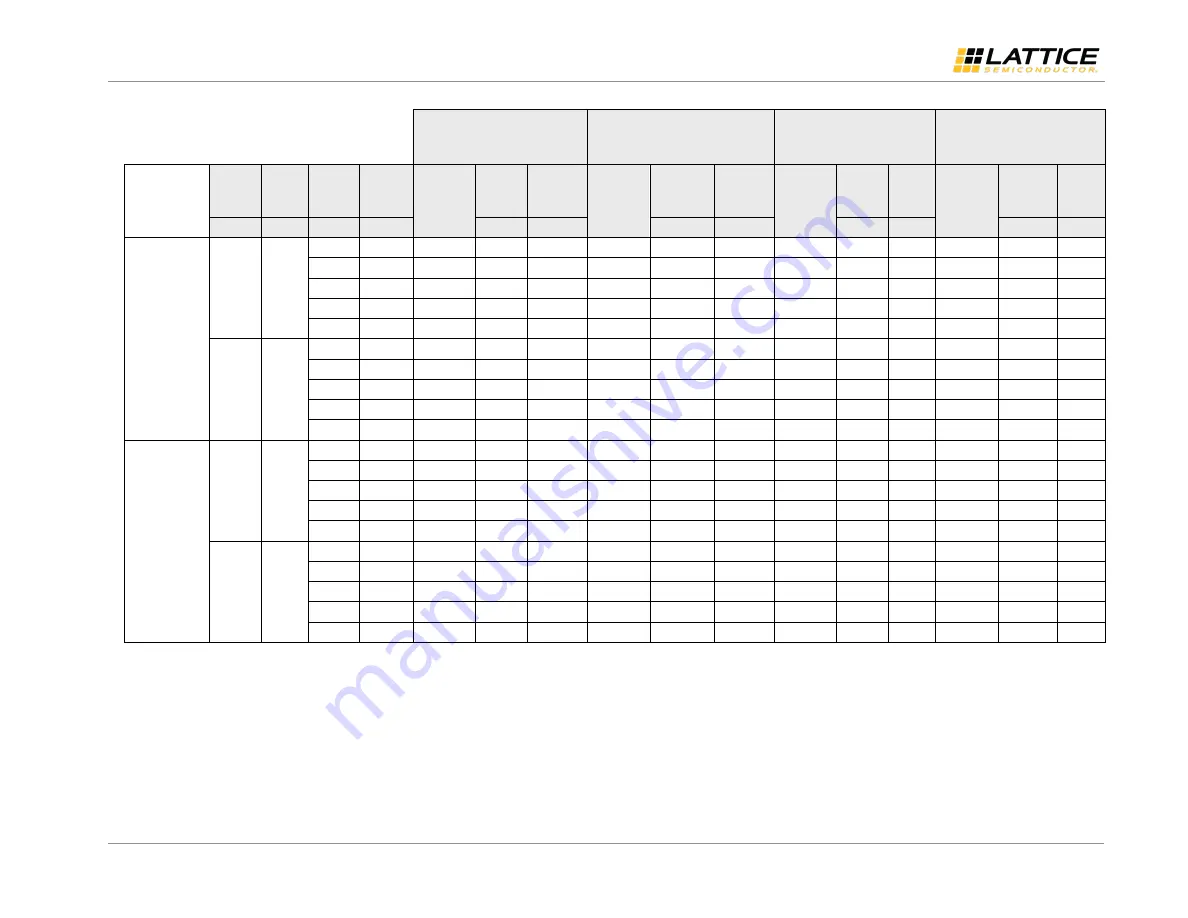

MIPI D-PHY Bandwidth Matrix Table

User Guide

© 2015-2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

26

FPGA-UG-02041-1.1

MachXO2 and MachXO3L

(523 Mbps for RX and 728

Mbps for TX I/O)

LatticeECP3 (467 Mbps for RX

and 698 Mbps for TX I/O)

ECP5/ECP5-5G (467 Mbps

for RX and 820 Mbps for

TX I/O)

CrossLink (898 Mbps for RX

and 1250 Mbps for TX I/O)

Resolution

Frame

Rate

Pixel

Clock

Color

Depth

Total

Data

Rate

Lane

Number

Line

Rate

Bit

Clock

Lane

Number

Line

Rate

Bit

Clock

Lane

Number

Line

Rate

Bit

Clock

Lane

Number

Line

Rate

Bit

Clock

Hz

MHz

Bits

Mbps

Mbps

MHz

Mbps

MHz

Mbps

MHz

Mbps

MHz

FHD

1920x1080p

(2200x1125)

60

148.5

8

1188

4

297

148.4

4

297

148.5

4

297

148.5

2

594

297

10

1485

4

371

185.6

4

371

185.6

4

371

185.6

—

—

—

16

2376

—

—

—

—

—

—

—

—

—

4

594

297

18

2673

—

—

—

—

—

—

—

—

—

—

—

—

24

3564

—

—

—

—

—

—

—

—

—

—

—

—

120

297

8

2376

—

—

—

—

—

—

—

—

—

4

594

297

10

2970

—

—

—

—

—

—

—

—

—

4

742.5

371

16

4752

—

—

—

—

—

—

—

—

—

—

—

—

18

5346

—

—

—

—

—

—

—

—

—

—

—

—

24

7128

—

—

—

—

—

—

—

—

—

—

—

—

UHD

3840x2160p

(4400x2250)

30

297

8

2376

4

594

1

297

4

594

1

297

4

594

1

297

4

594

297

10

2970

—

—

—

4

742.5

2

371

4

742.5

3

371

4

742.5

371

16

4752

—

—

—

—

—

—

—

—

—

—

—

—

18

5346

—

—

—

—

—

—

—

—

—

—

—

—

24

7128

—

—

—

—

—

—

—

—

—

—

—

—

60

594

8

4752

—

—

—

—

—

—

—

—

—

4

1188

594

10

5940

—

—

—

—

—

—

—

—

—

16

9504

—

—

—

—

—

—

—

—

—

—

—

—

18

10692

—

—

—

—

—

—

—

—

—

—

—

—

24

14256

—

—

—

—

—

—

—

—

—

—

—

—

Notes:

1.

Meeting Tx MIPI Alliance specification, Rx is not meeting MIPI Alliance requirement, and Tsu/Thd window can be calculated based on the

tSU/tHD Valid Window at Higher Data

section. Rx side is 0.17 UI (0.287 ns * 594 Mbps) for MachXO2/MachXO3L, 0.19 UI (0.321 ns * 594 Mbps) for LatticeECP3 andECP5/ECP-5G.

2.

Both Rx and Tx side not meeting MIPI Alliance specification, Rx Tsu/Thd window and Tx Tskew window can be calculated based on the

tSU/tHD Valid Window at Higher Data

and

Tskew Window at Higher Data Rate

sections. Tx side is 0.16 UI (0.215 ns * 742.5 Mbps), Rx side is 0.24 UI (0.321 ns * 742.5 Mbps).

3.

Meeting Tx MIPI Alliance specification, Rx is not meeting MIPI Alliance requirement, and Tsu/Thd window can be calculated based on

tSU/tHD Valid Window at Higher Data Rate

Rx side is 0.24 UI (0.321 ns * 742.5 Mbps).