ECP5 and ECP5-5G High-Speed I/O Interface

Technical Note

© 2014-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-TN-02035-1.3

35

6.2.2.

DLL-Compensated DQS Delay Elements

The DQS to and from the memory is connected to the DQS delay element inside the ECP5 and ECP5-5G device. The DQS

delay block receives the delay control code, DDRDEL, from the on-chip DDRDLL. The code generated by DDRDLL is

connected to the DQSBUF circuit to perform 90° read phase shift and 90° write phase shift. DDRDLL requires the

frequency reference from PLL, normally going through the Edge Clock tree.

ECP5 and ECP5-5G devices support one DDRDLL modules in each corner of the device. The DQSBUF modules that

receive the DDRDEL code from DDRDLL can either receive the code from the top or bottom DDRDLL on that side.

Hence, each side can support up to two different rate DDR memory interfaces.

Table 6.2. DDRDLL Connectivity

DDRDLL Location

Left DQSBUFs

Right DQSBUFs

DDRDLL_TR

—

X

DDRDLL_TL

X

—

DDRDLL_BR

—

X

DDRDLL_BL

X

—

The DQS received from the memory is delayed in the DQS delay element in the DQSBUF block, and this delayed DQS is

used to clock the first set stage DDR input registers.

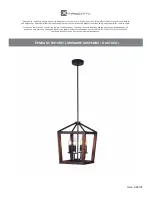

DQS

READ[1:0]

READCLKSEL[1:0]

ECLK

SCLK

DQSDEL

(90 Deg Delay Codefrom DDRDLL)

RDLOADN, RDMOVE, RDDIRECTION

(Read side Dynamic Margin Control)

WRLOADN, WRMOVE, WRDIRECTION)

(Write side Dynamic Margin Control)

PAUSE

DYNDELAY[7:0]

(Write Leveling Delay)

Preamble/Postamble Management

&

Burst Detect

FIFO Control & Datavalid

Generation

Read Side Slave Delay with

Dynamic Margin Control

Write Side Slave Delay with

Dynamic Margin Control

Write Leveling

BURSTDET

DATAVALID

RDPNTR[2:0]

WRPNTR[2:0]

DQSR90 (Read Side)

DQSW (Write Side)

DQSW270 (Write Side)

RDCFLAG

WRCFLAG

Figure 6.6. DQSBUF Block Functions

6.2.3.

Data Valid Module

The DQSBUF block generates a DATAVALID signal. This signal indicates the timing that the IDDR module drives the valid

read data transmitting to the FPGA fabric. DATAVALID is a level-sensitive active high signal and indicates that the read

data output from the IDDR module is valid while it is asserted high. The DATAVALID signal can stay asserted during the

IDDR module outputs back-to-back valid read data until all consecutive read operations are completed.