1-60 (No.49831)

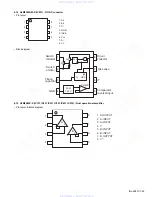

4.25 TMP91CW12AF4NB1 (IC501) : CPU

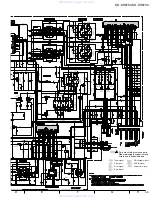

• Pin layout

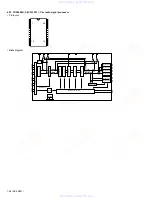

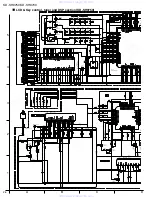

• Block diagram

1

25

75

51

100

26

76

50

Pin No

Symbol

I/O

Function

1

VREFL

-

Connect to ground

2

AVSS

-

Connect to ground

3

AVCC

-

Connect to 3.3V

4

CDON

O

CD power supply (3.3V) control

5

CDREQ

O

CD mechanism power supply request

6

CDMUTE

O

ICD mute

7

MP3RESET

O

CD MP3 reset

8

MP3STB

O

CD MP3 standby (H: Standby)

9 to 11

NC

-

Not connect

12

SW2

I

CD mechanism SW2

13

REST

I

CD mechanism rest SW

14 to 17

NC

-

Not connect

18

LCDCE/SO

O

Chip enable to LCD driver (Not connect)

19

LCDDA/SI

O

Data to LCD driver (Not connect)

20

LCDCK

O

Clock to LCD driver (Not connect)

21

BUSS0

I

JVC BUS data

22

BUSSI

O

JVC BUS data

23

BUSSCK

I/O

JVC BUS clock

24

AM0

Pull up to 3.3V

25

DVCC

-

Connect to 3.3V

26

X2

Crystal oscillator (24.576MHz)

Connect to ground

Crystal oscillator (24.576MHz)

Pull up to 3.3V

Reset

Not connect

Not connect

Not connect

Back up power supply detection (H: STOP mode)

36

SW1

I

CD mechanism SW1

37

P.DET

I

Main power off detection (H: HALT mode)

38 to 42

NC

-

Not connect

43

ALE

-

Not connect

44

BUS3

I/O

CD DSP data3

45

BUS2

I/O

CD DSP data2

46

BUS1

I/O

CD DSP data1

47

BUS0

I/O

CD DSP data0

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299