Application Note 1181

2

AN1181.1

November 28, 2011

actual loads can be used. It is STRONGLY recommended that the

power be turned off when attaching loads, due to the tight

spacing of the posts. The switcher outputs should be able to

provide at least 3A; monitor the FET temperature if you try to go

higher, to be sure the conditions will allow it. Make sure the input

power supply can source the amount of input current necessary

to drive the maximum loads to be tested.

The linear VOUT3 is especially sensitive to power dissipation

concerns; it will change as the user varies either the input

voltage, the output voltage, and/or the load current. The

equation used is PV

OUT3

= (V

IN3

-V

OUT3

)*I

OUT3

. The PNP bipolar

will also be rated for how well the power is dissipated from the

package and spread out on the board; this is another variable

that the user must keep in mind for their design and layout.

JP1 is used to disable VOUT1, by shorting SS/EN1 to GND. JP2

does the same function for VOUT2.

The switching frequency is controlled by a resistor (R4) on the RT

pin, to GND. Refer to the datasheet for the curve of resistor

values versus frequency.

Each output voltage is determined by a resistor divider from the

output to its FB pin to GND. See the

ISL6442 datasheet

for the

formulas to calculate the values. Note that there are some

limitations; the switchers can approach 100% duty, but will be

limited by dead time, r

DSON

of the FETs at maximum load,

switching frequency, etc. The maximum values are limited by the

VIN available (if you want go higher, check the ratings of the FETs,

and other output components to be sure they can handle it). The

minimum output voltage will be just above the 0.6V internal

reference. The maximum output voltage for the linear is limited

by the VIN3 and the LCDR pin (which is biased from 5V). Thus, the

maximum output voltage is close to the 5V set on the board; it is

not recommended to go higher. The minimum voltage will also

be just above the 0.6V internal reference.

Performance Waveforms

These figures depict the ISL6442EVAL1Z performance during

typical operational situations, as well as during fault conditions.

Loading of the output can be most easily done via an electronic

load; however, other methods can work as well.

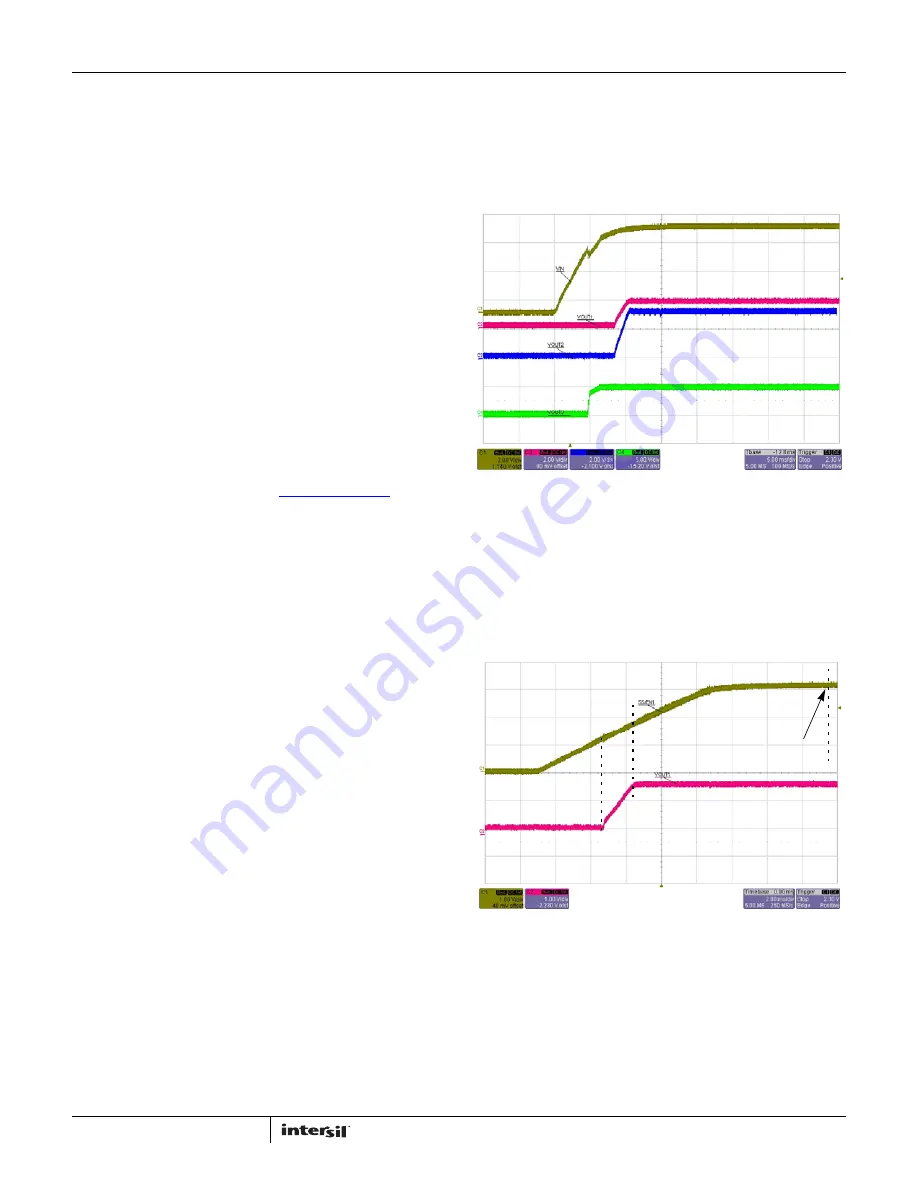

Figure 3 shows a typical power-up sequence, with all inputs

connected to a single VIN = VIN3 = 6V. When VCC exceeds its

POR rising trip point (~4.4V), the IC is enabled, and the linear

VOUT3 comes up almost immediately. Meanwhile, the two SS/EN

pins start charging (not shown), but the outputs do not start

ramping until the SS/EN pins ~1V; then both switcher outputs

start their soft-start ramps at the same time. In this case, both

outputs track each other initially; this is accomplished by

selecting the ratio of SS/EN capacitors to match their output

voltages. The ramp times shown are on the order of a few

milliseconds, as determined by the SS/EN capacitors on the

board.

Figure 4 shows the detail soft start waveform of PWM1 (PMW2

would be similar). The full SS/EN1 ramp is shown; the output

doesn’t start to ramp until the SS/EN passes the ~1V threshold

for Enable. The output ramps from zero to full scale, while

SS/EN1 ramps from 1.0V to 1.6V. Finally, the EN/SS1 keeps

ramping up to ~3.2V, at which point the ramp is considered done

(the PGOOD timer would start from this point, if both outputs

ramps were done).

FIGURE 3. TYPICAL POWER-UP WAVEFORMS WITH VIN

CH4 VOUT3

(5V/DIV)

CH3 VOUT2

(2V/DIV)

CH2 VOUT1

(2V/DIV)

CH1 VIN

(2V/DIV)

5ms/DIV; VIN3 = VIN

CH1 OUT1

(1V/DIV)

CH1 EN/SS1

(1V/DIV)

2ms/DIV

FIGURE 4. PWM1 SOFT-START

~3.2V