10/10/06

CONFIDENTIAL INFORMATION-DO NOT COPY

4

October 10, 2006 11:23 am

SupraHD-760-DTS-GEN-v1.0-Preliminary Release

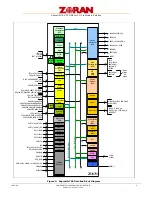

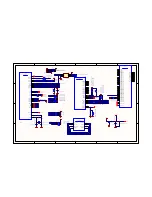

Figure 3: SupraHD-760 Detailed Block Diagram

ZR39760

SADR[13:0], SBS[1:0]_n

SDQM[3:0]

SRAS_n, SCAS_n, SWE_n

SCLK, SCLK_n, SCKE

SDQS[3:0],

SDATA[15:0]

SVREF

Memory

Interface Unit

(MIF)

16

4

3

3

4

16

Embedded

Processing Unit

(EPC)

MIPS 4Kec

I Cache

D Cache

MMU

EJTAG

Ctlr.

JTAG

Ctlr.

Counters/

Timers

6

Transport

Processing Unit

(TRP)

Xport I/F

Xport Demux

Video Capture

Unit

HDMI

NTSC/PAL

Decoder

8

Audio

Processing Unit

(APU)

Display

Processor

(DPC)

Graphics

MPEG2 Decode

Unit

(VDEC)

uController

(MCU)

Sequencer

(MCE)

Flex Bus Unit

(FBU)

MI

F BU

S

(6

4b

)

I2C Ctlr. 1

I2C Ctlr. 2

I2C Ctlr. 3

GPIO

2

2

2

4

IRR

1

I2C0C, I2C0D

I2C1C, I2C1D

I2C2C, I2C2D

GPIO[3:0]

IRR

UART0

2

UART0_TX, UART0_RX

BVCI

Modified

Guest Bus

5

GADR[4:0]

GDAT[7:0]

6

GCS_n[5:0]

1

GWS_ACK

5

GDIR, GOE_n, GIOWR_n, GIORD_n, GWE_n

4

GIRQ[3:0]

CLKIN,

CLKOUT

BV

C

I/A

V

C

I BU

S (6

4b

)

RESET_n

Video I/F

29

13

HDMI_SCL, HDMI_SDA,

HDMI_CEC, HDMI_HPD, HDMI_REXT,

HDMI_D0P, HDMI_D0N, HDMI_D1P,

HDMI_D1N, HDMI_D2P, HDMID2N,

HDMI_CLKP, HDMI_CLKN

TDO, TDI

TCK, TMS

TRST_N, TAPSEL

10

PV

C

I

B

U

S

(6

4b

)

Link List

CLKGEN

DVCXO

PLL

2

BLT

UART1

2

UART1_TX, UART1_RX

ACLK

BCLK, LRCLK

ADATAO[2:0]

ADATAI[2:0]

IEC958

PIXOUT[23:0],PCLK, DEN, OSDP,

AFHSI, AFVSI

HDMI

PHY

VFE_YIN, VFE_CIN,

VFE_CVBS,VFE_REFP, VFE_REFN,

VFE_VCM, VFE_IBEXT, VFE_BG

Unique 128-bit

ID

LVDS Output

19

LVDS_C_P, LVDS_C_N,

LVDS_D[7:0]_P, LVDS_D[7:0]_N

LVDS_REXT

L/R

Audio

DACs

4

ADATAO[2:0]

ADATAI[2]

Shared

with the

I2S

signals

AGC

4

IF_AGC, AGC_SENSE, RF_AGC,

PWM_OUT

Demod

7

IFE_AIMP, IFE_VREFP, IFE_VREFN,

IFE_AINN, IFE_RBIAS, IFE_VCM, IFE_VINBIAS

Smart

Antenna

3

SADATA, GPIOx, GPIO,

8

4

TSO_CLK, TSO_FRAME,

TSO_VALID, TSO_DATA

4

TSI_CLK, TSI_FRAME,

TSI_VALID, TSI_DATA

SPI

5

SPI_CLK, SPI_SI, SPI_SO,

SPI_HOLD, SPI_WEN