Document Number: 002-14826 Rev. *G

Page 5 of 65

PRELIMINARY

CYW43903

1. Overview

1.1 Introduction

The Cypress CYW43903 is a single-chip device that provides the highest level of integration for an embedded system-on-a-chip with

integrated IEEE 802.11 b/g/n MAC/baseband/radio and a separate ARM Cortex-R4 applications processor. It provides a small form-

factor solution with minimal external components to drive down cost for mass volumes and allows for an embedded system with

flexibility in size, form, and function. Comprehensive power management circuitry and software ensure that the system can meet the

needs of highly embedded systems that require minimal power consumption and reliable operation.

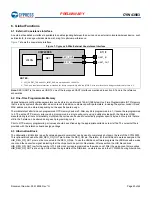

shows the interconnect of all the major physical blocks in the CYW43903 and their associated external interfaces, which are

described in greater detail in Applications Subsystem External Interfaces.

Figure 2. Block Diagram and I/O

Note:

Another SPI interface can be defined by reconfiguring GPIO_8 through GPIO_11 and another CSC interface can be defined

by reconfiguring GPIO_12 and GPIO_13 (see

).

APPS Subsystem

WLAN Subsystem

CYW43903

SPI Flash

GPIO[16:0]

2x 2-Wire UART

4-Wire UART

SPI/CSC

CSC

JTAG/SWD

WAKE

RF TX

RF RX

Switch Control

Antenna Diversity

VDDIOs

GND

ARM Cortex‐R4

160 MHz

32 KB I‐cache

32 KB D‐cache

1 MB SRAM

640 KB ROM

ARM Cortex‐R4

160 MHz

448 KB ROM TCM

576 KB SRAM TCM

802.11n

1x1

2.4 GHz