3. RapidIO Lanes > Port and Lane Initialization Sequence

CPS-1848 User Manual

81

June 2, 2014

Formal Status

This document is confidential and is subject to an NDA.

Integrated Device Technology

3.4.1.3

Bit Error Rate Measurement for RapidIO Compliant Data

Bit error rate testing is facilitated by use of the Error Management Extensions registers. The physical layer error management

extensions registers can be used to count the number of received bit errors on the link. To configure a port to count bit errors,

perform the steps outlined in the following table.

Once the above steps are completed for a port, the

.ERR_RATE_CNTR field can be read to

determine the number of errors seen since the counter was last cleared to 0.

The above algorithm reports all detectable errors for a port. If a port has multiple lanes, it is not possible to attribute the errors

to a particular lane. To monitor errors on an lane-by-lane basis, use the ERR_8B10B field of the

.

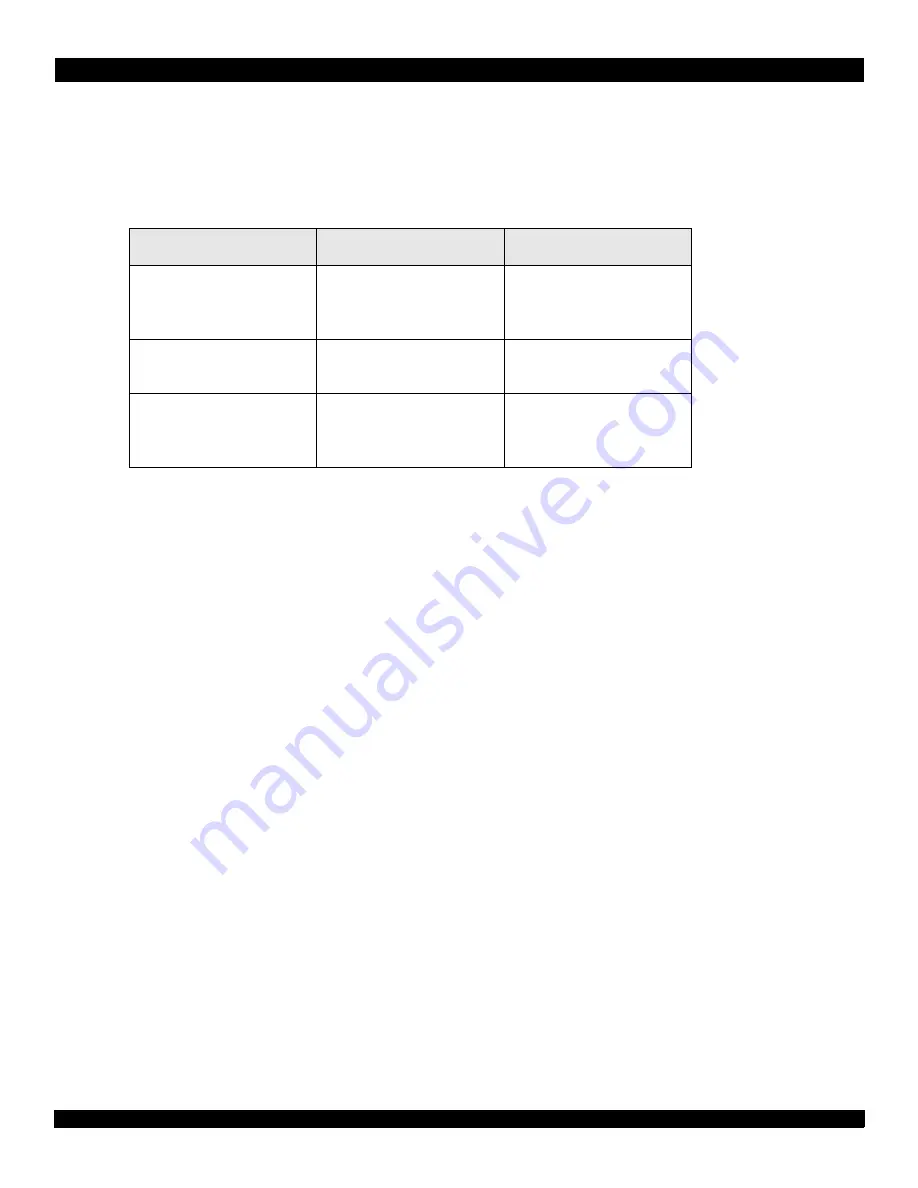

Table 24: Configuring Bit Error Measurement

Step

Offset

Value

Enable all Rx error events

0x1044 (Port 0)

Port {0..17} Error Rate Enable

0x004E8015

Clear counter to 0, allow

counter to reach 0xFF

0x1068 (Port 0)

0x00030000

Disable event notification

0x106C (Port 0)

0x00000000