Rev. 1.10

46

November 04, 2019

Rev. 1.10

47

November 04, 2019

HT45F5Q-3

Battery Charger Flash MCU

HT45F5Q-3

Battery Charger Flash MCU

Bit 0

WRF

: WDT control register software reset flag

0: Not occurred

1: Occurred

This bit is set to 1 by the WDT Control register software reset and cleared by the

application program. Note that this bit can only be cleared to 0 by the application

program.

Watchdog Timer Operation

The Watchdog Timer operates by providing a device reset when its timer overflows. This means

that in the application program and during normal operation the user has to strategically clear the

Watchdog Timer before it overflows to prevent the Watchdog Timer from executing a reset. This is

done using the clear watchdog instruction. If the program malfunctions for whatever reason, jumps

to an unknown location, or enters an endless loop, the clear WDT instruction will not be executed in

the correct manner, in which case the Watchdog Timer will overflow and reset the device. There are

five bits, WE4~WE0, in the WDTC register to offer the enable/disable control and reset control of

the Watchdog Timer. The WDT function will be disabled when the WE4~WE0 bits are set to a value

of 10101B while the WDT function will be enabled if the WE4~WE0 bits are equal to 01010B.

If the WE4~WE0 bits are set to any other values, other than 01010B and 10101B, it will reset the

device after a delay time,

t

SRESET

. After power on these bits will have a value of 01010B.

WE4~WE0 Bits

WDT Function

10101B

Disable

01010B

Enable

Any other value

Reset MCU

Watchdog Timer Enable/Disable Control

Under normal program operation, a Watchdog Timer time-out will initialise a device reset and set

the status bit TO. However, if the system is in the SLEEP or IDLE Mode, when a Watchdog Timer

time-out occurs, the TO and PDF bits in the status register will be set high and only the Program

Counter and Stack Pointer will be reset. Three methods can be adopted to clear the contents of the

Watchdog Timer. The first is a WDT software reset, which means a certain value except 01010B

and 10101B written into the WE4~WE0 bits, the second is using the Watchdog Timer software clear

instruction, the third is via a HALT instruction.

There is only one method of using software instruction to clear the Watchdog Timer. That is to use

the single “CLR WDT” instruction to clear the WDT.

The maximum time-out period is when the 2

18

division ratio is selected. As an example, with a

32kHz LIRC oscillator as its source clock, this will give a maximum watchdog period of around 1

second for the 2

1

5

division ratio, and a minimum timeout of 8ms for the 2

8

division ration.

“

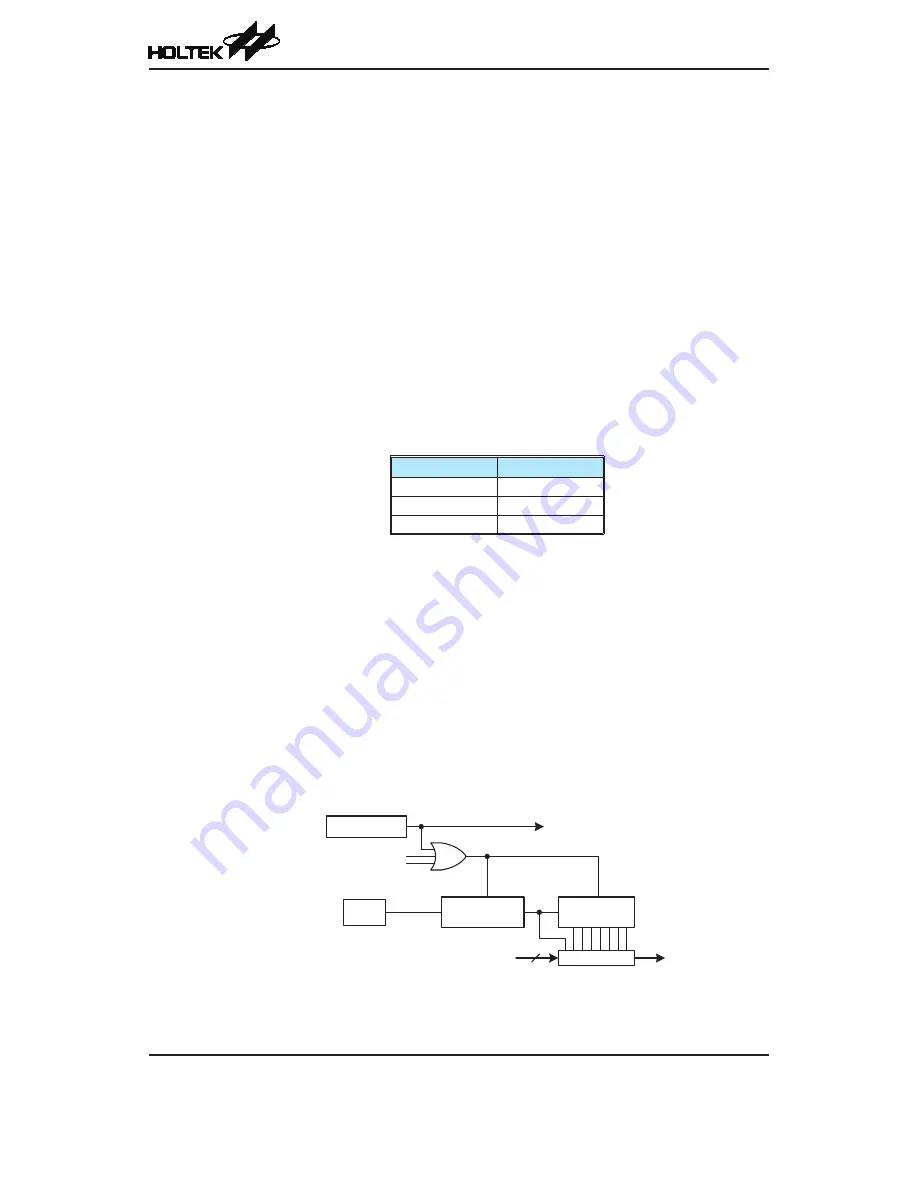

CLR WDT

”

Instruction

WE4~WE0 bits

WDTC Register

Reset MCU

f

LIRC

CLR

“

HALT

”

Instruction

LIRC

8-stage Divider

WDT Prescaler

f

LIRC

/2

8

8-to-1 MUX

WS2~WS0

WDT Time-out

(2

8

/f

LIRC

~2

18

/f

LIRC

)

Watchdog Timer