Содержание MP-1802

Страница 1: ......

Страница 20: ......

Страница 55: ......

Страница 77: ......

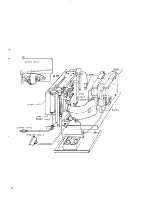

Страница 80: ...2 M D D FDD card connec power unit ASSAC cird powe r cord buffer cabl e ryt ...

Страница 82: ......

Страница 83: ... p f f r 1 P x B e f f 1 n j r i r M E t N 4 r _ 4 u trHE E l t 7E9 E ...