M 100-CD MKII

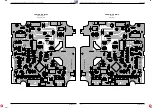

Schaltpläne und Druckplattenabbildungen / Circuit Diagrams and Layout of PCBs

GRUNDIG Service

2 - 13

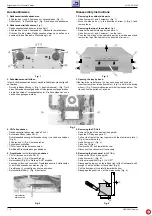

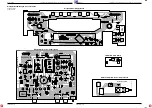

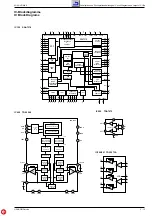

IC-Blockdiagramme

IC Block Diagrams

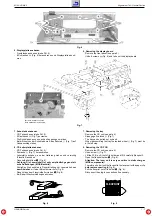

IC400 TDA1549

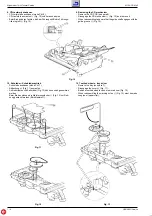

IC500 TDA7072

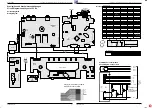

IC100 SAA7378

-

+

6

7

-

+

5

4

8

9

10

12

11

3

2

1

16

13

14

15

DATA

TEST

BCK

WS

FILTCL

VOL

VREF

VSSA

VDDA

VDDO

VSSO

FILTCR

VOR

N.C.

VSSD

VDDD

Control

and

Timing

FIR Filter

7th Order Halfband Filter

Linear Interpolator

Data Encoder

2nd Order

Noisehaper

6x Oversampling

(Sample and Hold)

Data Encoder

2nd Order

Noisehaper

6x Oversampling

(Sample and Hold)

Left Output

Switches

16 (4–bit)

Calibrated

Current

Sources

16 (4–bit)

Calibrated

Current

Sinks

Right Output

Switches

16 (4–bit)

Calibrated

Current

Sources

16 (4–bit)

Calibrated

Current

Sinks

Reference

Source

OP1

OP2

TDA 1549

16 fs

96 fs

+

-

VDD

TDA7072

GND

1

2

3

6

8

5

OUT+

OUT-

IN+

IN-

SAA7378

60

61

25

24

50

21

22

3

4

5

7

45

31

27

15

17

10

18

14

43

64

44

33

34

55

8

9

53

26

37

57

35

48

52

51

13

36

28

58

38

20

23

29

62

63

42

41

40

30

47

59

2

19

11

6

32

39

49

56

1

12

16

46

SERIAL

OUTPUT

VDDA2

SUBCODE

CONTROL

MICRO

GEN

END

DECODER

TIMING

VREF

FRONT

INTERFACE

PROCESSOR

VDDA1

PROCESSOR

VRL

R1

R2

VRH

VSSA1

D3

D4

IREFT

HFIN

HFREF

STATUS

SELPLL

CL4

ISLICE

INTERFACE

INTERFACE

CORRECTOR

VDD2P

PEAK

DETECT

KILL

VDD1P

AUDIO

PROCESSOR

VERSATILE

INTERFACE

PLL

EFM

SRAM

RAM

&

DEMOD

VDD3C

EBU

DIGITAL

ADDRESSER

INTERFACE

CONTROL

DATA

MICROPROCESSOR

TEST

ERROR

FLAGS

MOTOR

STAGE

VSSA2

SUB

RCK

NC1

RA

VSSA3

C2FAIL

SBSY

SFSY

SCLK

WCLK

DATA

MISC

CFLG

DOBM

LDON

RESET

IREF

D1

D2

SL

MOT2

MOT1

VSS3

VSS2

VSS4

VSS1

FO

CL11

CROUT

CRIN

KILL

V5

V4

V3

V2

SILD

V1

RAB

SDA

TEST3

SCL

TEST2

TEST1

CL16

ADC

1

2

5

6

7

9

10

12

13

14

16

+

+

+

+

+

-

+

-

VDD

TDA7073A

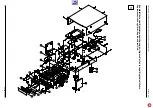

IC200/201 TDA7073A