4 Signal Description

IPUG781-1.5.1E

9(12)

4

Signal Description

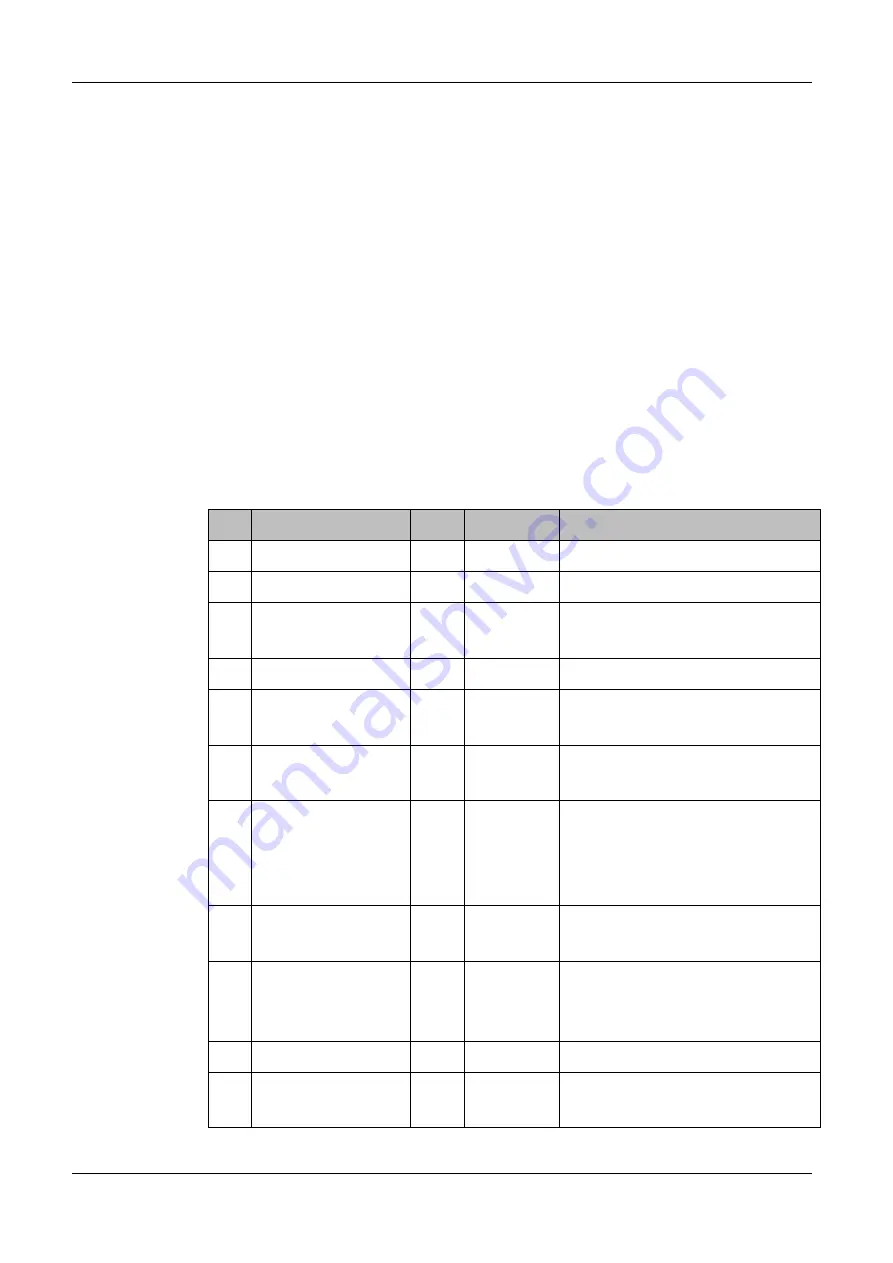

A description of Gowin USB 2.0 SoftPHY IP signals is as shown in Table

Table 4-1 Signal Description

No. Signal Name

I/O

Data Width Description

1

clk_i

I

1

Input clock signal (60MHz)

2

fclk_i

I

1

Input clock signal (480MHz)

3

rst_i

I

1

Asynchronous reset signal resets

the state machine inside of PHY.

4

pll_locked_i

I

1

pll lock signal generating fclk_i

5

utmi_data_out_i

I

8

Data input, 8-bit parallel data

transmit bus.

6

utmi_txvalid_i

I

1

Transmit data valid indicator,

active-high.

7

utmi_txready_o

O

1

Transmit data ready signal,

indicating that PHY can receive the

data to be transmitted from the

controller end.

8

utmi_data_in_o

O

8

Data output, 8-bit parallel data

receive bus.

9

utmi_rxactive_o

O

1

Rx data active, indicating that PHY

detects the SYNC signal and then

starts receiving data.

10

utmi_rxvalid_o

O

1

Rx data valid, active-high.

11

utmi_rxerror_o

O

1

Receive data error, active high

indicates receive error.

Содержание USB 2.0 SoftPHY IP

Страница 1: ...Gowin USB 2 0 SoftPHY IP User Guide IPUG781 1 5 1E 07 20 2022 ...

Страница 19: ......