MB95630H Series

62

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 4 RESET

4.1 Reset Operation

4.1

Reset Operation

When a reset source occurs, the CPU immediately stops the process being

executed and enters the reset release wait state. When the reset is released,

the CPU reads mode data and the reset vector from the Flash memory (mode

fetch). When the power is switched on or when the device is released from a

reset in subclock mode, sub-CR clock mode, or stop mode, the CPU performs

mode fetch after the oscillation stabilization wait time has elapsed.

■

Reset Sources

There are five reset sources for the reset.

●

External reset

An external reset is generated if "L" level is input to the external reset pin (RST).

An external input reset signal is received asynchronously with the operating clock of the

microcontroller via the internal noise filter and then generates an internal reset signal that is

synchronized with the machine clock to initialize the internal circuit. Therefore, the operating

clock of the microcontroller is necessary for initializing the internal circuit. In order to operate

with the external clock, external clock signals must be input. However, the external pins

(including I/O ports and peripheral functions) are reset asynchronously. In addition, there is a

standard value of the pulse width for external reset input. If the value is below the standard

value, a reset signal may not be accepted.

The standard value is shown in the device data sheet. Design an external reset circuit that

satisfies the standard value.

●

Software reset

Writing "1" to the software reset bit of the standby control register (STBC:SRST) generates a

software reset.

●

Watchdog reset

After the watchdog timer starts, a watchdog reset is generated if the watchdog timer is not

cleared within a predetermined period of time.

●

Power-on reset

A power-on reset is generated when the power is switched on.

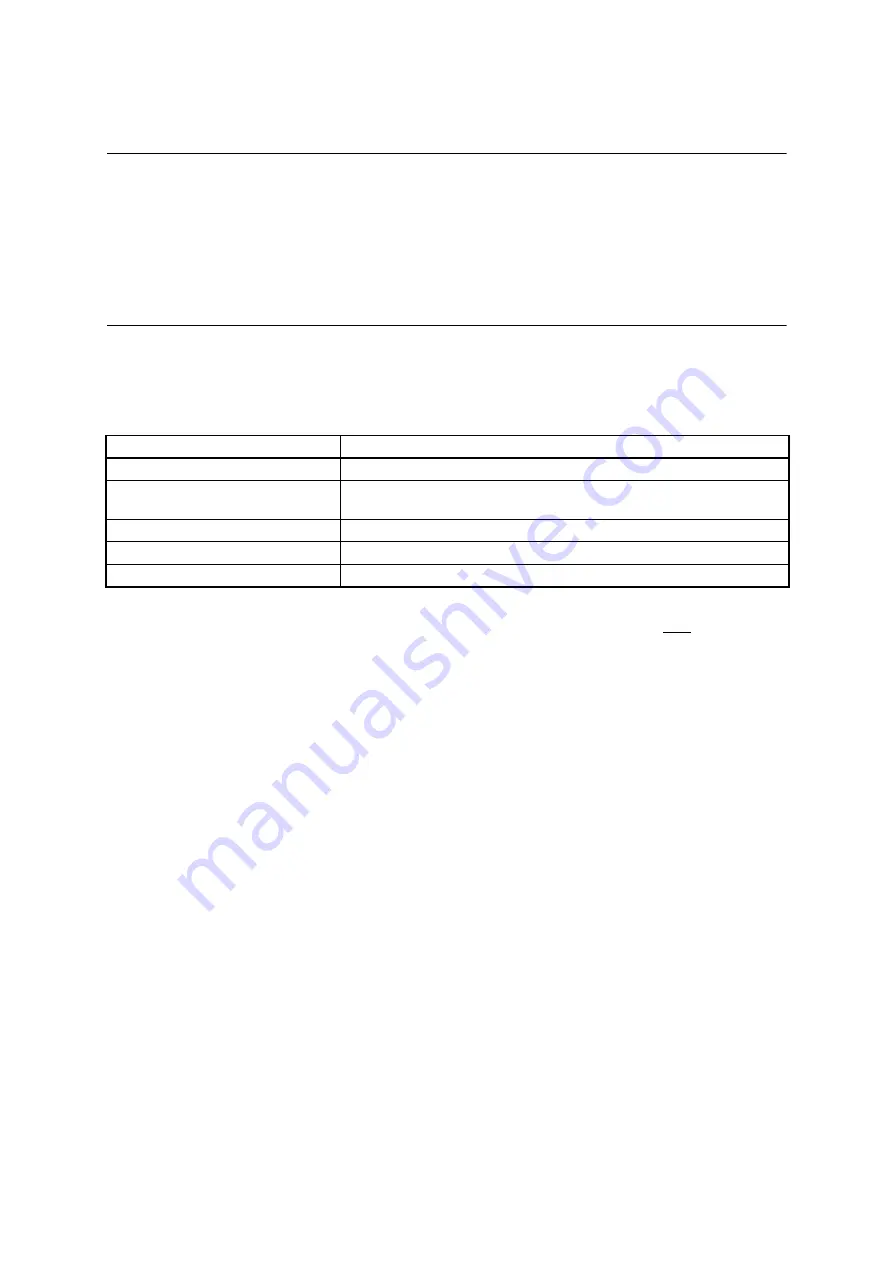

Table 4.1-1 Reset Sources

Reset source

Reset condition

External reset

"L" level is input to the external reset pin.

Software reset

"1" is written to the software reset bit in the standby control register

(STBC:SRST).

Watchdog reset

The watchdog timer overflows.

Power-on reset

The power is switched on.

Low-voltage detection reset (optional)

The supply voltage falls below the detection voltage.

Содержание MB95630H Series

Страница 2: ......

Страница 4: ......

Страница 8: ...iv ...

Страница 20: ...xvi ...

Страница 106: ...MB95630H Series 86 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E CHAPTER 6 I O PORT 6 2 Configuration and Operations ...

Страница 282: ...MB95630H Series 262 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E CHAPTER 14 LIN UART 14 8 Notes on Using LIN UART ...

Страница 642: ...MB95630H Series 622 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E APPENDIX A Instruction Overview A 5 Instruction Map ...

Страница 644: ......