MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

427

CHAPTER 21 MULTI-PULSE GENERATOR

21.6 Registers

21.6.1

16-bit MPG Output Control Register (Upper)

(OPCUR)

The 16-bit MPG output control register (upper) (OPCUR) controls the write

timing interrupt, the data transfer method and the DTTI pin.

■

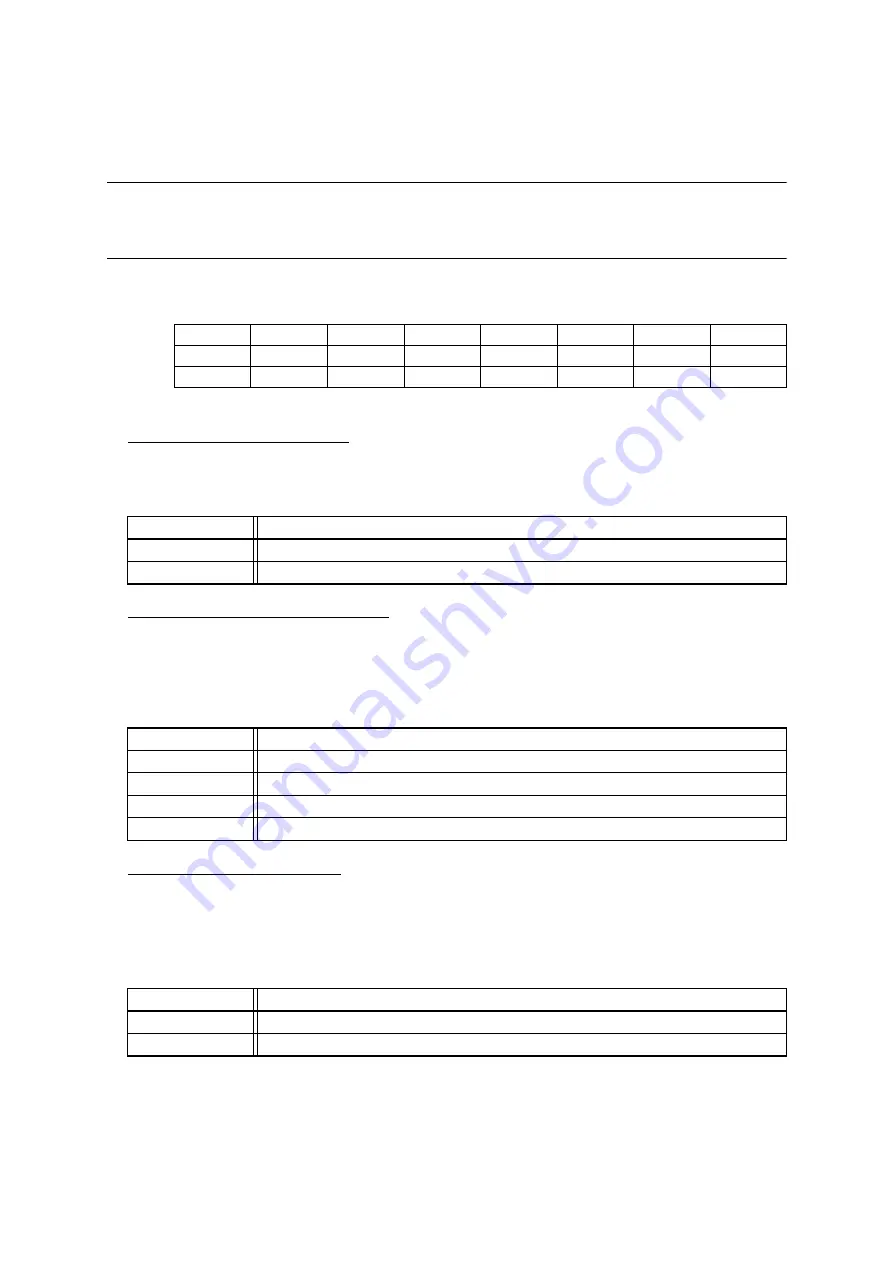

Register Configuration

■

Register Functions

[bit7] DTIE: DTTI control enable bit

This bit enables or disables the DTTI pin input.

It enables the DTT1 pin to control the output levels of the OPT5 to OPT0 pins. The software can set the

inactive level for an OPTx pin according to the setting of the PDRx register corresponding to that OPTx pin.

[bit6] DTIF: DTTI interrupt request flag bit

This bit is the DTTI input interrupt request flag.

With the DTTI control enable bit (DTIE) already set to "1", when a falling edge of DTTI is detected, this bit

is set to "1" and a DTTI interrupt is generated.

Writing "0" to this bit clears it. Writing "1" to this bit has no effect on operation.

When read by the read-modify-write (RMW) type of instruction, this bit always returns "1".

[bit5] NRSL: Noise filter enable bit

This bit selects the noise cancellation function to be used when the DTTI pin input is enabled.

The noise cancellation circuit starts the internal n-bit counter when an active level is input (the value of n can

be 2, 3, 4 or 5, which depends on the setting of D[1:0] bits in the noise cancellation control register). If the

active level is held until the counter overflows, the circuit accepts input from the DTTI pin. Therefore, the

pulse width of noise that can be cancelled is about 2

n

machine cycles.

Note: When the noise cancellation circuit is enabled, the DTTI pin input becomes invalid in a mode such as

stop mode in which the internal clock is stopped.

bit

7

6

5

4

3

2

1

0

Field

DTIE

DTIF

NRSL

OPS2

OPS1

OPS0

WTIF

WTIE

Attribute

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0

bit7

Details

Writing "0"

Disables using the DTTI pin input to control the output level.

Writing "1"

Enables using the DTTI pin input to control the output level.

bit6

Details

Reading "0"

Indicates that no falling edge of DTTI has been detected.

Reading "1"

Indicates that a falling edge of DTTI has been detected.

Writing "0"

Clears this bit.

Writing "1"

Has no effect on operation.

bit5

Details

Writing "0"

The DTTI pin input will not pass through the noise filter.

Writing "1"

The DTTI pin input will pass through the noise filter.

Содержание MB95630H Series

Страница 2: ......

Страница 4: ......

Страница 8: ...iv ...

Страница 20: ...xvi ...

Страница 106: ...MB95630H Series 86 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E CHAPTER 6 I O PORT 6 2 Configuration and Operations ...

Страница 282: ...MB95630H Series 262 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E CHAPTER 14 LIN UART 14 8 Notes on Using LIN UART ...

Страница 642: ...MB95630H Series 622 FUJITSU SEMICONDUCTOR LIMITED MN702 00009 1v0 E APPENDIX A Instruction Overview A 5 Instruction Map ...

Страница 644: ......