68

CHAPTER 3 INTERRUPTS

3.5.3

Multiple interrupts

As a special case, no hardware interrupt request can be accepted while data is being

written to the I/O area. For MB90390 Series, this includes the address ranges "00

H

" to

"BF

H

", ("3100

H

" to "31FF

H

", "3300

H

" to "33FF

H

",) "3500

H

" to "35FF

H

", "3700

H

" to

"37FF

H

", "3900

H

" to "39FF

H

", "3B00

H

" to "3BFF

H

", "3D00

H

" to "3DFF

H

" and "3F00

H

" to

"3FFF

H

". This is intended to prevent the CPU from operating falsely because of an

interrupt request issued while an interrupt control register for a resource is being

updated. If an interrupt occurs during interrupt processing, a higher-level interrupt is

processed first.

■

Multiple Interrupts

The F

2

MC-16LX CPU supports multiple interrupts. If an interrupt of a higher level occurs while another

interrupt is being processed, control is transferred to the high-level interrupt after the currently executing

instruction is completed. After processing of the high-level interrupt is completed, the original interrupt

processing is resumed. An interrupt of the same or lower level may be generated while another interrupt is

being processed. If this happens, the new interrupt request is suspended until the current interrupt

processing is completed, unless the ILM value or I flag is changed by an instruction.

The extended intelligent I/O service cannot be activated from multiple sources; while an extended

intelligent I/O service is being processed, all other interrupt requests or extended intelligent I/O service

requests are suspended.

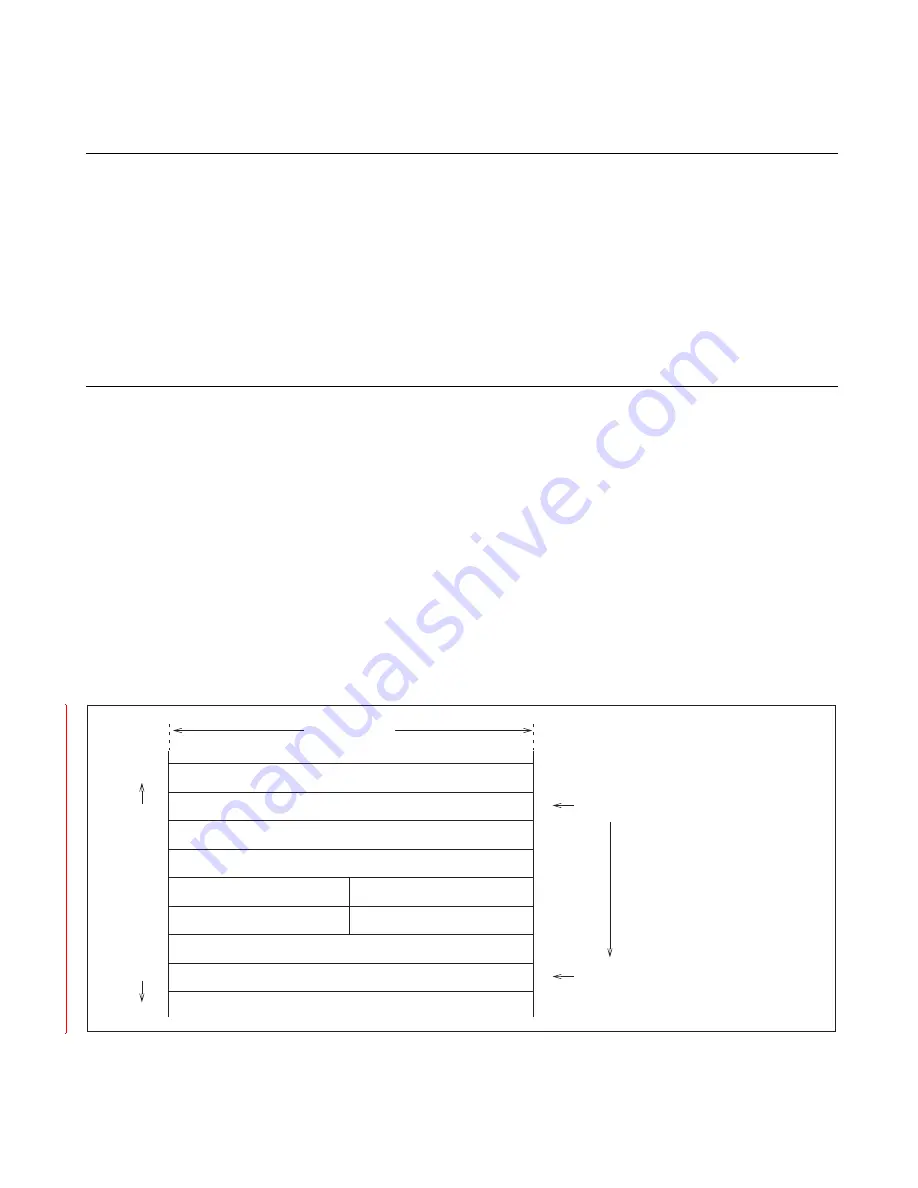

Figure 3.5-2 shows the order of the registers saved in the stack.

Figure 3.5-2 Registers Saved in Stack

"H"

"L"

MSB

LSB

AH

AL

PC

PS

ADB

PCB

DTB

DPR

Word (16 bits)

SSP (SSP value before interrupt)

SSP (SSP value after interrupt)

Содержание MB90390 Series

Страница 2: ......

Страница 4: ......

Страница 17: ...xiii APPENDIX D List of Interrupt Vectors 690 INDEX 695 ...

Страница 18: ...xiv ...

Страница 132: ...104 CHAPTER 5 CLOCKS ...

Страница 152: ...124 CHAPTER 6 CLOCK MODULATOR ...

Страница 210: ...182 CHAPTER 11 TIME BASE TIMER ...

Страница 218: ...190 CHAPTER 12 WATCHDOG TIMER ...

Страница 264: ...236 CHAPTER 14 16 BIT RELOAD TIMER WITH EVENT COUNT FUNCTION ...

Страница 274: ...246 CHAPTER 15 WATCH TIMER ...

Страница 306: ...278 CHAPTER 17 DTP EXTERNAL INTERRUPTS ...

Страница 338: ...310 CHAPTER 18 8 10 BIT A D CONVERTER ...

Страница 364: ...336 CHAPTER 19 UART0 UART1 ...

Страница 398: ...370 CHAPTER 20 UART2 UART3 Figure 20 5 2 ORE Set Timing Receive data RDRF ORE ...

Страница 432: ...404 CHAPTER 20 UART2 UART3 ...

Страница 482: ...454 CHAPTER 22 SERIAL I O ...

Страница 560: ...532 CHAPTER 24 STEPPING MOTOR CONTROLLER ...

Страница 582: ...554 CHAPTER 27 ROM MIRRORING MODULE ...

Страница 632: ...604 CHAPTER 29 EXAMPLES OF SERIAL PROGRAMMING CONNECTION ...

Страница 722: ...694 APPENDIX ...

Страница 723: ...695 INDEX The index follows on the next page This is listed in alphabetic order ...

Страница 740: ......