Hardware Documentation efus™A9X+ efus™A9Xr2

| 22

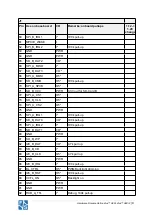

4.11 RGB LCD

87

BL_CTRL

3.3V CMOS PWM output for Backlight dimming

89

VCFL_ON

CMOS 3.3V high active Backlight on

93

LCD_CLK

RGB LCD clock

97

LCD_HSYNC

RGB LCD HSYNC

99

LCD_VSYNC

RGB LCD VSYNC

103

LCD_R0

Red0

105

LCD_R1

Red1

107

LCD_R2

Red2

109

LCD_R3

Red3

111

LCD_R4

Red4

113

LCD_R5

Red5

117

LCD_G0

Green0

119

LCD_G1

Green1

121

LCD_G2

Green2

123

LCD_G3

Green3

125

LCD_G4

Green4

127

LCD_G5

Green5

131

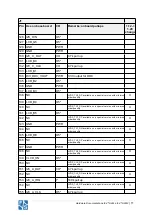

LCD_B0

Blue0

133

LCD_B1

Blue1

135

LCD_B2

Blue2

137

LCD_B3

Blue3

139

LCD_B4

Blue4

141

LCD_B5

Blue5

145

LCD_DE

Data enable

149

VLCD_ON

CMOS 3.3V high active LCD power on

Because all signals does work with 3.3V TTL level and high speed, high EMI radiation will be

generated. Signals should be routed as short as possible and shielding is necessary.

Please also refer the efus design guide for connecting displays with more color bits.