© 2011 Fairchild Semiconductor Corporation

21

FEBFSQ500L_H257v1 • Rev. 1.0.1

Customer

P/N:

TRN-0246

DATE 08/12/2008

Version A

Page

2/3

2.Schematic:

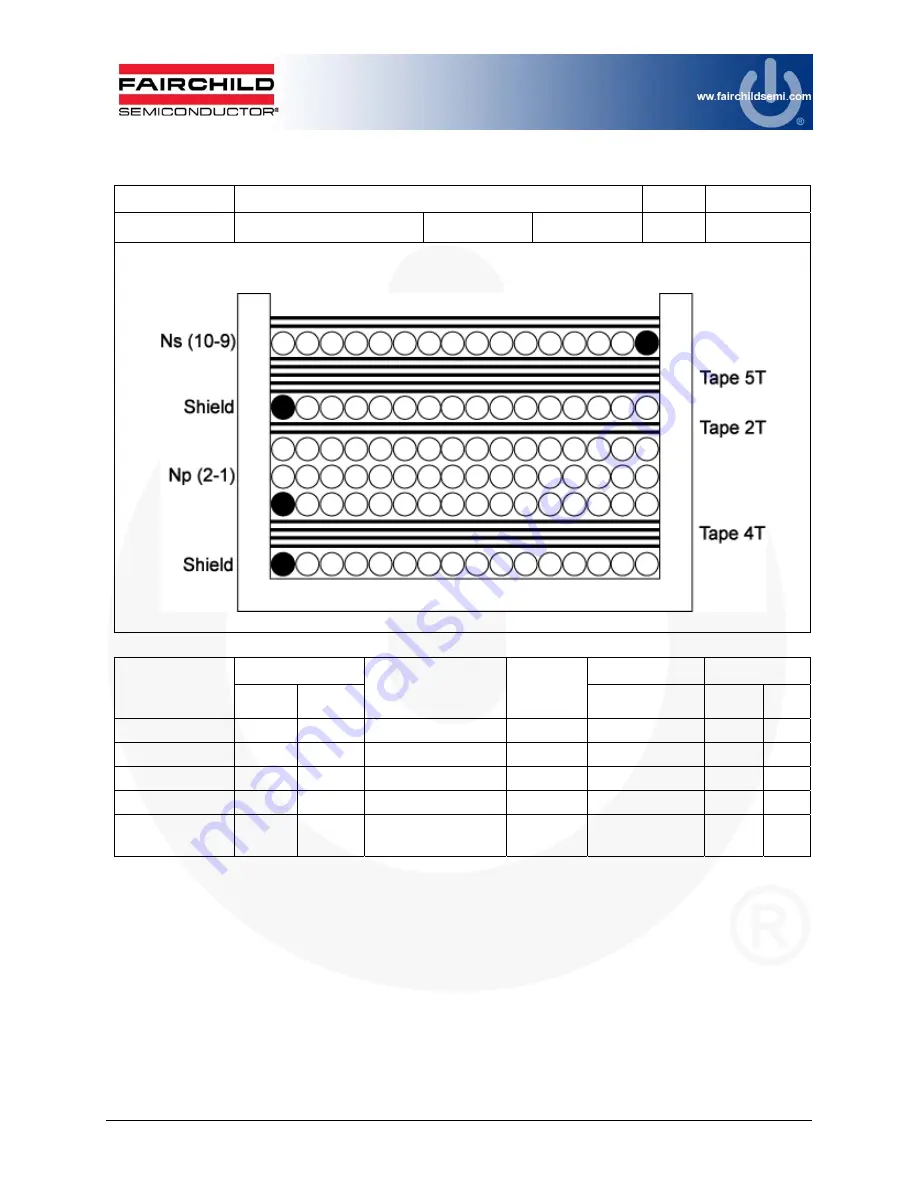

NO

TERMINAL

WIRE T

S

INSULATION BARRIER

S F

T

S

S

w1 1

x

0.15*1

46 4

w2 2

1

0.2*1

104 2

w3 1

x

0.15*1

46 5

w4 10

9

TEX-E 0.4*1

9 2

CORE

ROUNDING TAPE

3