12 I

2

C (I2C)

S1C17F13 TeChniCal Manual

Seiko epson Corporation

12-15

(Rev. 1.0)

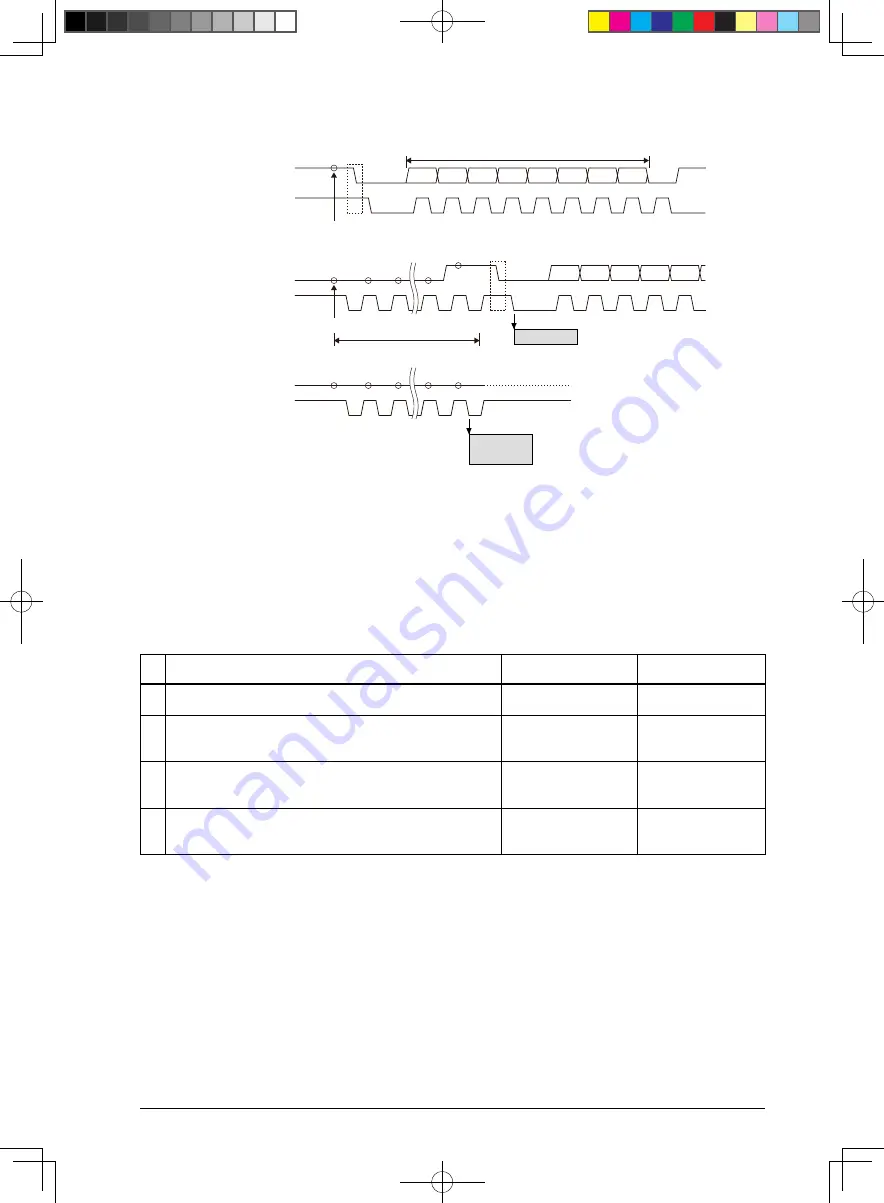

Normal operations

STARTIF = 1

ERRIF = 1

STARTIF = 1

SDA

SCL

START

condition

START

condition

Slave a R/W

SDA check

1

2

n

When SDA = LOW is detected

SDA

SCL

Bus clearing operation

SDA check

(n

≤

9)

1

2

10

SDA

SCL

4.8.1 Automatic Bus Clearing Operation

Figure 12.

Error Detection

12.4.9

The I2C includes a hardware error detection function.

Furthermore, the I2C

n

INTF.SDALOW and I2C

n

INTF.SCLLOW bits are provided to allow software to check whether

the SDA and SCL lines are fixed at low. If unintended low level is detected on SDA or SCL, a software recovery pro-

cessing, such as I2C Ch.

n

software reset, can be performed.

The table below lists the hardware error detection conditions and the notification method.

4.9.1

Table 12.

Hardware Error Detection Function

No.

Error detecting period/timing

I

2

C bus line monitored and

error condition

Notification method

1 While the I2C Ch.

n

controls SDA to high for sending address,

data, or a NACK

SDA = low

I2C

n

INTF.ERRIF = 1

2 <Master mode only> When 1 is written to the I2C

n

CTL.TX-

START bit while the I2C

n

INTF.BSY bit = 0

SCL = low

I2C

n

INTF.ERRIF = 1

I2C

n

CTL.TXSTART = 0

I2C

n

INTF.STARTIF = 1

3 <Master mode only> When 1 is written to the I2C

n

CTL.TXS-

TOP bit while the I2C

n

INTF.BSY bit = 0

SCL = low

I2C

n

INTF.ERRIF = 1

I2C

n

CTL.TXSTOP = 0

I2C

n

INTF.STOPIF = 1

4 <Master mode only> When 1 is written to the I2C

n

CTL.TX-

START bit while the I2C

n

INTF.BSY bit = 0 (Refer to “Automatic

Bus Clearing Operation.”)

SDA

Automatic bus clearing

failure

I2C

n

INTF.ERRIF = 1

I2C

n

CTL.TXSTART = 0

I2C

n

INTF.STARTIF = 1