19 SPi

S1C17624/604/622/602/621 TeChniCal Manual

Seiko epson Corporation

19-7

SPTBE is set to 0 when transmit data is written to the SPI_TXD

x

register (transmit data buffer), and is

set to 1 when the data is transferred to the shift register (when transmission starts).

Transmission data must be written to the SPI_TXD

x

register when this bit is 1.

SPi Ch.

x

Transmit Data Register (SPi_TXD

x

)

Register name address

Bit

name

Function

Setting

init. R/W

Remarks

SPi Ch.

x

Transmit Data

Register

(SPi_TXD

x

)

0x4322

(16 bits)

D15–8 –

reserved

–

–

–

0 when being read.

D7–0 SPTDB[7:0] SPI transmit data buffer

SPTDB7 = MSB

SPTDB0 = LSB

0x0 to 0xff

0x0 R/W

D[15:8] Reserved

D[7:0]

SPTDB[7:0]: SPi Transmit Data Buffer Bits

Sets transmit data to be written to the transmit data buffer. (Default: 0x0)

In master mode, transmission is started by writing data to this register. In slave mode, the contents of

this register are sent to the shift register and transmission begins when the clock is input from the mas-

ter.

SPTBE/SPI_ST

x

register is set to 1 (empty) as soon as data written to this register has been transferred

to the shift register. A transmit buffer empty interrupt is generated at the same time. The subsequent

transmit data can then be written, even while data is being transmitted.

Serial converted data is output from the SDO

x

pin, with the bit set to 1 as High level and the bit set to 0

as Low level.

note: Make sure that SPEN is set to 1 before writing data to the SPI_TXD

x

register to start data trans-

mission/reception.

SPi Ch.

x

Receive Data Register (SPi_RXD

x

)

Register name address

Bit

name

Function

Setting

init. R/W

Remarks

SPi Ch.

x

Receive Data

Register

(SPi_RXD

x

)

0x4324

(16 bits)

D15–8 –

reserved

–

–

–

0 when being read.

D7–0 SPRDB[7:0] SPI receive data buffer

SPRDB7 = MSB

SPRDB0 = LSB

0x0 to 0xff

0x0

R

D[15:8] Reserved

D[7:0]

SPRDB[7:0]: SPi Receive Data Buffer Bits

Contains the received data. (Default: 0x0)

SPRBF/SPI_ST

x

register is set to 1 (data full) as soon as data is received and the shift register data has

been transferred to the receive data buffer. A receive buffer full interrupt is generated at the same time.

Data can then be read until subsequent data is received. If receiving the subsequent data is completed

before the register has been read out, the new received data overwrites the contents.

Serial data input from the SDI

x

pin is converted to parallel, with the High level bit set to 1 and the Low

level bit set to 0. The data is the loaded into this register.

This register is read-only.

SPi Ch.

x

Control Register (SPi_CTl

x

)

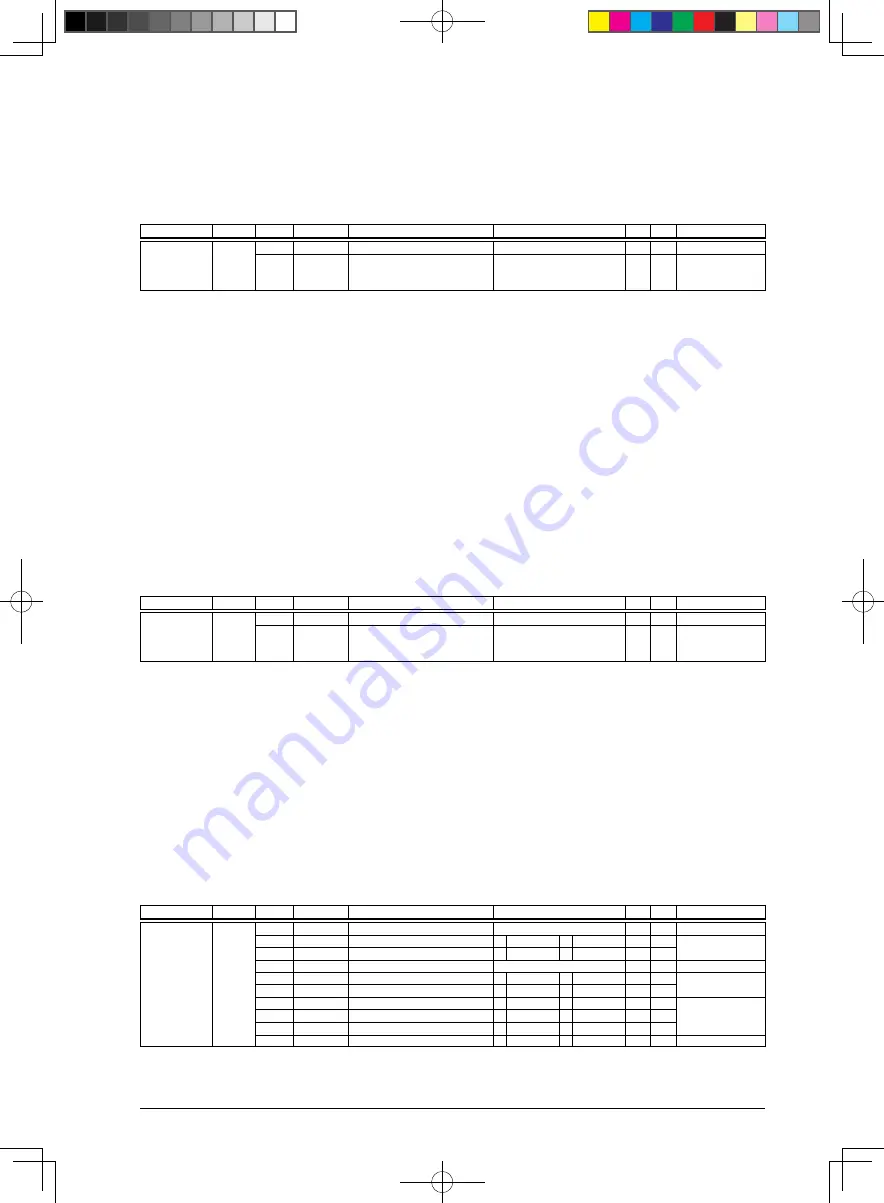

Register name address

Bit

name

Function

Setting

init. R/W

Remarks

SPi Ch.

x

Con-

trol Register

(SPi_CTl

x

)

0x4326

(16 bits)

D15–10 –

reserved

–

–

–

0 when being read.

D9

MClK

SPI clock source select

1 T16 Ch.1

0 PCLK/4

0

R/W

D8

MlSB

LSB/MSB first mode select

1 LSB

0 MSB

0

R/W

D7–6 –

reserved

–

–

–

0 when being read.

D5

SPRie

Receive data buffer full int. enable 1 Enable

0 Disable

0

R/W

D4

SPTie

Transmit data buffer empty int. enable 1 Enable

0 Disable

0

R/W

D3

CPha

Clock phase select

1 Data out

0 Data in

0

R/W These bits must be

set before setting

SPEN to 1.

D2

CPOl

Clock polarity select

1 Active L

0 Active H

0

R/W

D1

MSSl

Master/slave mode select

1 Master

0 Slave

0

R/W

D0

SPen

SPI enable

1 Enable

0 Disable

0

R/W

note: In the S1C17602/621, do not access to the SPI_CTL

x

register while SPBSY/SPI_ST

x

register is

set to 1 or SPRBF/SPI_ST

x

register is set to 1 (while data is being transmitted/received).