H O S T I N T E R F A C E

Data Device Corporation

DS-BU-67301B-G

1/14

64

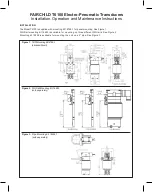

Figure 24. Synchronous, Non-Multiplexed Address - 32-bit Single-Word Register Read

Timing

Figure 24 Notes:

1. When nSELECT is asserted (low), the

Total-AceXtreme®

is selected for this

data transfer. nSELECT should be asserted throughout the entire transfer

cycle, and de-asserted high at the end of the transfer.

2. For register transfers, the value of the CPU_WORD_EN[1:0] inputs must be

‘11’.

3. For a single-word register read access, CPU_nSTOP asserts (low)

simultaneous with nDATA_RDY, and de-asserts (high) on the host clock cycle

following nSELECT returning high.

nDATA_RDY

CPU_DATA

CPU_WORD_EN[1:0]

RD_nWR

MEM_nREG

CPU_ADDR

nDATA_STRB

nSELECT

CPU_nSTOP

HOST_CLK

tOHZ

tOH

tSTPD

tDD

tSH

Address

tCLK

Data

tRDD

tRDD

tSTPD

tSS

tCS

tCH

tAS

tAS

tAS

tAS

tAH

tAH

tAH

tAH

tSHC

tWait

CPU_nLAST