DM9163

Layout Guide

Version: DM9163-LG-V10

5

May 5, 2014

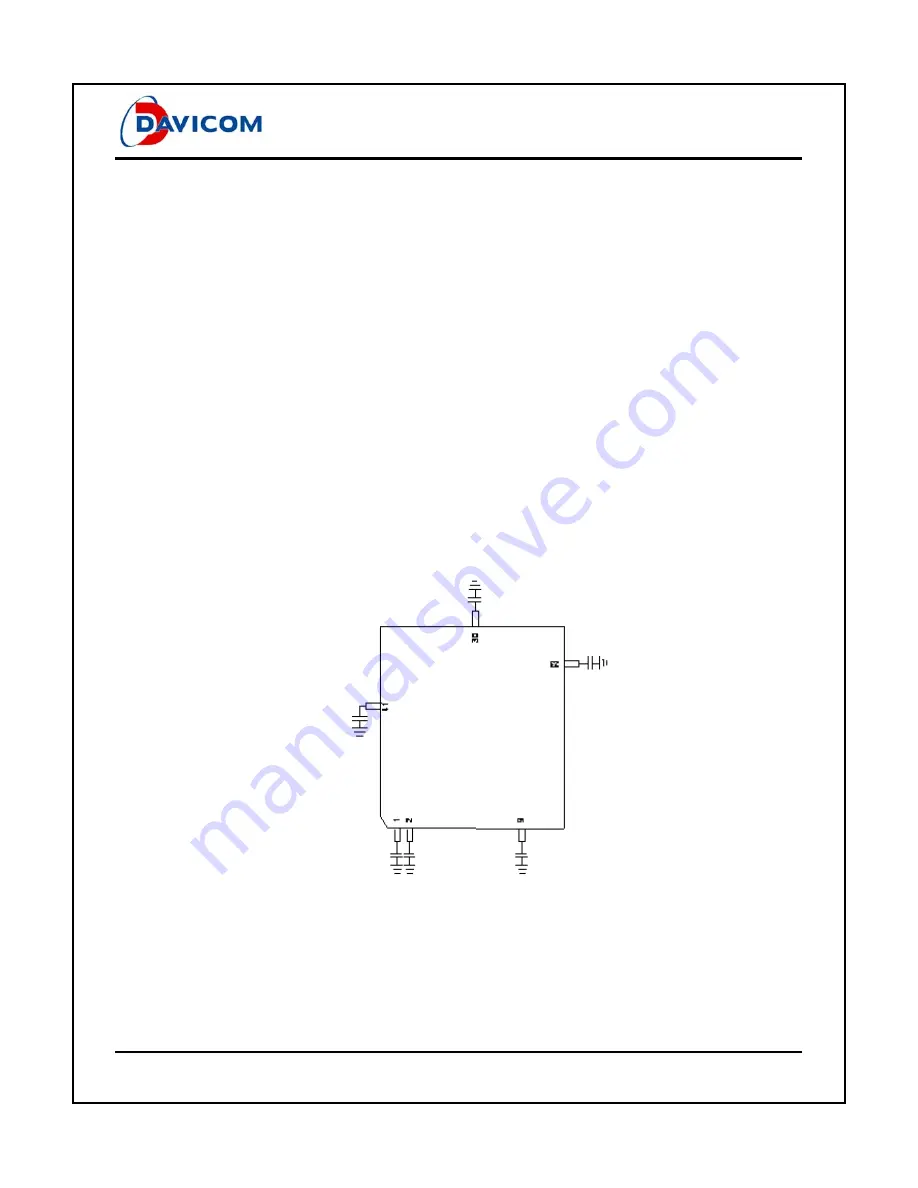

2. Power Supply Decoupling Capacitors

•

Place all the decoupling capacitors for all power supply pins as close as possible to the power pads of the

DM9163 (no more than 2.5mm from the above mentioned pins). The recommended decoupling capacitor is

0.1

μ

F or 0.01

μ

F.

•

The PCB layout and power supply decoupling should provide sufficient decoupling to achieve the following

when measured at the device:

(1) All DVDDs and AVDDs should be within 50mV peak to peak of each other,

(2) All DGNDs and AGNDs should be within 50mV peak to peak of each other.

(3) The resultant AC noise voltage measured across each DVDD/DGND set and AVDD/AGND set should be

less than 100mV peak to peak.

•

The

0.1-0.01

μ

F decoupling capacitor should be connected between each DVDD/DGND set and

AVDD/AGND set and be placed as close as possible to the power pins of DM9163. The conservative

approach is to use two decoupling capacitors on each DVDD/DGND set and AVDD/AGND set. One 0.1

μ

F is

for low frequency noise, and the other 0.01

μ

F is for high frequency noise on the power supply.

•

The 3.3V connection to the transmit center tap of the magnetic has to be well decoupled to minimize

common mode noise injection from the power supply into the twisted pair cable. It is recommended that a

0.01

μ

F decoupling capacitor should be placed between the center tap 3.3V to AGND ground plane. This

decoupling capacitor should be placed as close as possible to the center tap of the magnetic.10 uF or 47 uF

Capacitor should be connected between each 3.3V and AGND.

Figure 2

DM9163