35

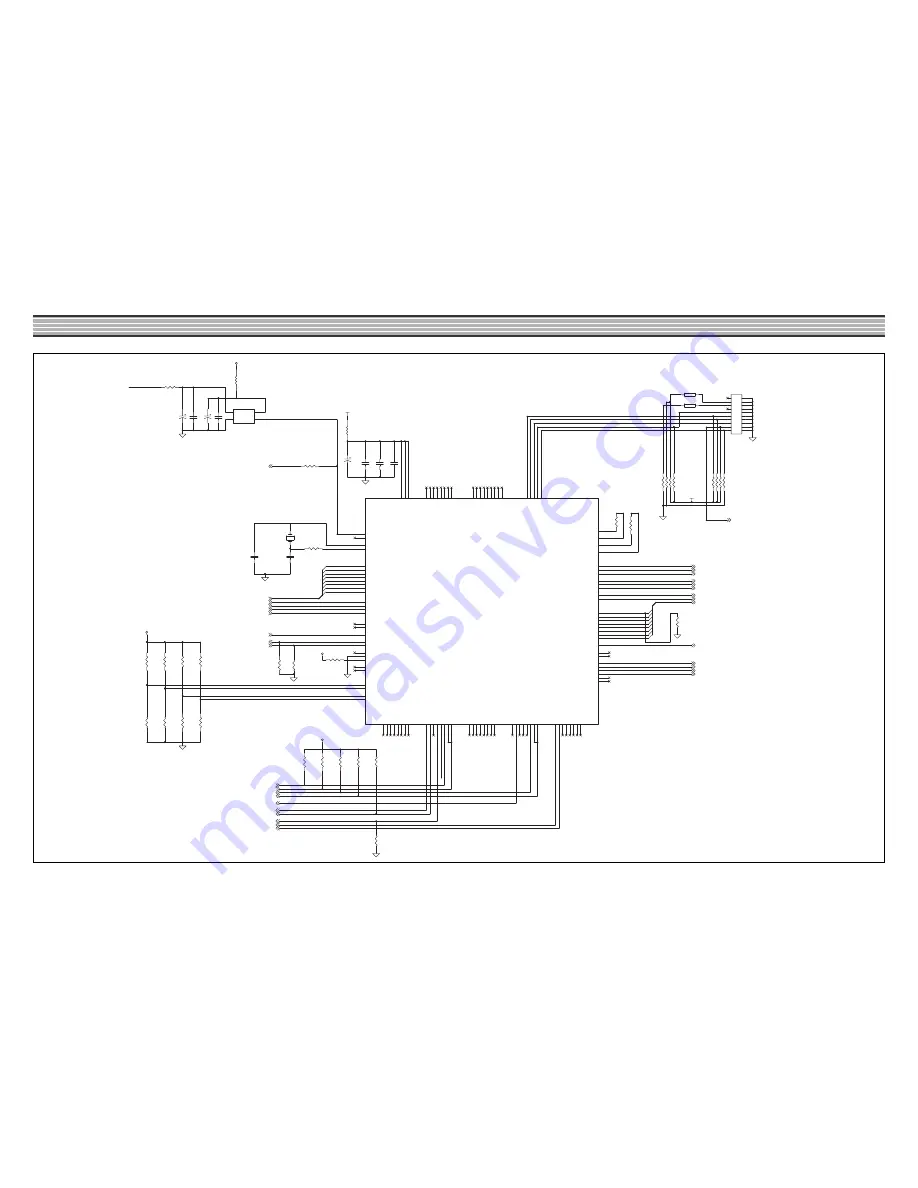

SCHEMATIC DIAGRAM

NOT INCLUDE MASS PRODUCTION

JTAG PORT

BS1 BS0

1 1 : BOOT FROM

ROM 8 BIT

1 0 : BOOT FROM

ROM 16 BIT

0 1 : BOOT FROM

ROM 32 BIT

0 0 : BOOT FRO

M OSLINK

---------------

--------

PWM27MHz

K

F

IR_

TS

[7

..0

]

KFIR_TS6

SD

A(M

AST

ER

)

KFIR_TS0

KFIR_TS5

KFIR_TS[7..0]

PWM27MHz

KFIR_TS2

KFIR_TS4

KFIR_TS1

KFIR_TS7

KFIR_TS3

SC

L(M

AST

ER

)

R

ESET

_KF

IR

A

_

MUTE

SC

L(SLAVE)

HDD_RESET

BS0

BS1

SP1

SP0

DV_OUT2

DV_OUT7

DV_OUT6

DV_OUT5

DV_OUT1

DV_OUT3

DV_OUT[7..0]

DV_OUT4

DV_OUT0

DV

_

O

UT[7

..0

]

SD

A(SLAVE)

M

AST

ER

_R

EAD

D

V_SW

AV_SW1

AUDIO_MCLK

2,8

AUDIO_DATA

2,8

AUX_CLK

2

PVR R

9

PVR G

9

PVR B

9

PVR CV

9

AUDIO_LRCLK 2,8

PVR C

9

PVR Y

9

AUDIO_SCLK

2,8

SDA_MA

2,3

SCL_MA

2,3

A_MUTE

7

RESET_KFIR

7

HDD_RESET

7

KFIR_TS[7..0]

3

KFIR_CLK

3

KFIR_VALID

3

KFIR_SYNC

3

KFIR_ERROR

3

PVR_RESET

7

SDA_SL

11

SCL_SL

11

INT0

7

ST20_RESET

7

WAKE_UP

11

MASTER_READ

11

DV_SW

2

DV_OUT[7..0]

2

V_SYNC

2

H_SYNC

2

AV_SW1

8

HS_27MHz

12

VCC(+5V)

+3_3V_E

+3_3V_D

+3_3V_D

+3_3V_D

+3_3V_D

P602

CON20(0.1"DIL)

1

3

5

7

9

11

13

15

17

19

2

4

6

8

10

12

14

16

18

20

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

R556

5.1K

R536

5.1K

C566

10u/50V

R535

5.1K

R576

4.7k

R577

NONE

R572

NONE

X504

32.768KHz

R573

4.7k

PJ??

0R

R505

NONE

R557

5.1K

C569

22pF

R575

4.7k

C568

0.1uF

R524

11K5 1%

R555

5.1K

R521

5.1K

R574

NONE

C572

0.1uF

C570

0.1uF

R570

4.7k

R529

4.7K

R571

NONE

R553

5.1K

R621

NONE

PJ??

0R

C567

10u/50V

R622

NONE

R554

5.1K

R533

5.1K

R623

5.1K

R558

5.1K

R520

330K

R626

10K

X602

27MHz

8

4

5

1

VCC

GND

OUT

TS

R624

5.1K

IC601_A

ST5512

G1

W6

A8

U12

L20

K17

L1

Y10

V11

W10

B3

A3

U3

U4

U2

R3

R2

R4

M2

M3

D8

D12

D16

L17

R17

U11

U7

D4

T4

L4

T2

P2

T1

P1

P3

N1

N3

M1

N2

N4

J19

J20

H17

K1

K2

R19

V4

W4

Y4

V5

W5

Y5

U6

V6

Y6

V7

W7

W8

Y8

D5

C4

V9

V2

W1

V3

W2

Y1

W3

Y2

Y3

Y7

U8

V8

W9

Y9

U1

0

V10

C3

B4

A4

L2

A1

B1

B2

A2

L3

Y11

W11

P18

P19

P20

N18

N19

N20

M17

M18

M19

M20

L18

L19

H4

M4

J4

J3

J2

H3

J1

E1

F1

F2

F3

G2

G3

G4

H1

C2

C1

D3

D2

D1

E4

E3

E2

H2

VClamp1

VClamp2

VClamp3

CLK

PLL_MULT0

PLL_MULT1

RST#

CPU_Analyse/Trig_In

CPU_RST

Error_Out/Tig_Out

INT0

WAKE_UP

R_OUT

G_OUT

B_OUT

C_OUT

CV_OUT

Y_OUT

H_SYNC

V_SYNC

DV_OUT0

DV_OUT1

DV_OUT2

DV_OUT3

DV_OUT4

DV_OUT5

DV_OUT6

DV_OUT7

CFC

OSD_EN

I_REF_DAC_RGB

I_REF_DAC_YCC

V_REF_DAC_RGB

V_REF_DAC_YCC

SCLK/AC3_STB

PCM_DATA/AC3_DATA

MCLK

LRCLK/AC3_WORD_CLK

AC3_REQ

AC3_PTS_STB

Boot_Source0

Boot_Source1

CPU_CLK_OUT

LP_CLK_IN

LP_CLK_OUT

AUX_CLK_OUT

PI

O0_0

PI

O0_1

PI

O0_2

PI

O0_3

PI

O0_4

PI

O0_5

PI

O0_6

PI

O0_7

PI

O1_0

PI

O1_1

PI

O1_2

PI

O1_3

PI

O1_4

PI

O1_5

PI

O1_6

PI

O1_7

PI

O2_0

PI

O2_1

PI

O2_2

PI

O2_3

PI

O2_4

PI

O2_5

PI

O2_6

PI

O2_7

PI

O3_0

PI

O3_1

PI

O3_2

PI

O3_3

PI

O3_4

PI

O3_5

PI

O3_6

PI

O3_7

PI

O4_0

PI

O4_1

PI

O4_2

PI

O4_3

PI

O4_4

PI

O4_5

PI

O4_6

PI

O4_7

Link_IN

Link_OUT

TS_DATA0

TS_DATA1

TS_DATA2

TS_DATA3

TS_DATA4

TS_DATA5

TS_DATA6

TS_DATA7

TS_SYNC

TS_VALID

TS_ERROR

TS_CLK

TTXT_VSYNC#

TTXT_HSYNC#

TDI

TDO

TMS

TCK

TRS

T#

1284_D

AT

A0/

AV_D

AT

A0

1284_D

AT

A1/

AV_D

AT

A1

1284_D

AT

A2/

AV_D

AT

A2

1284_D

AT

A3/

AV_D

AT

A3

1284_D

AT

A4/

AV_D

AT

A4

1284_D

AT

A5/

AV_D

AT

A5

1284_D

AT

A6/

AV_D

AT

A6

1284_D

AT

A7/

AV_D

AT

A7

1284_SELEC

T

_

IN

#

1284_I

N

IT

#

/AV_PAC

KET

_T

AG3

1284_F

AU

LT

#/

AV_PAC

KET

_T

AG2

1284_AU

T

O_F

EED

#/

AV_PAC

KET

_T

AG1

1284_SELEC

T

/AV_PAC

KET

_T

AG0

1284_P_ER

R

O

R

/AV_VALI

D

1284_BU

SY/

AV_SYN

C

1284_AC

K#/

AV_C

LK

1284_ST

R

OBE#/

AV_ER

R

O

R

R552

5.1K

R525

4.7K

C571

0.1uF

R522

5.1K

C573

0.1uF

R551

5.1K

R625

10K

C591

10pF

C565

10u/50V

R523

11K5 1%

Содержание DHD-4000D

Страница 30: ...29 BLOCK DIAGRAM VIDEO BLOCK ...

Страница 32: ...31 BLOCK DIAGRAM TUNER BLOCK ...

Страница 40: ...39 SCHEMATIC DIAGRAM ...

Страница 44: ...43 SCHEMATIC DIAGRAM SCHEMATIC DIAGRAM ...

Страница 45: ...44 COMPONENTS LOCATION GUIDE ON PCB BOTTOM VIEW ...

Страница 49: ......

Страница 66: ...686 AHYEON DONG MAPO GU SEOUL KOREA C P O BOX 8003 SEOUL KOREA DAEWOO ELECTRONICS Corp ...