Service manual CP-785AF

- 30 -

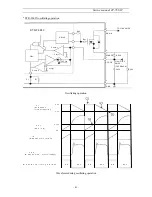

FUNCTIONAL DESCRIPTION OF VIDEO PROCESSOR Vision IF amplifier

The vision IF amplifier can demodulate signals with positive and negative modulation. The PLL

demodulator is completely alignment-free.

The VCO of the PLL circuit is internal and the frequency is fixed to the required value by using the

clock frequency of the

µ

-Controller/Teletext decoder as a reference. The setting of the various

frequencies is made by the controlling software in subaddress 27H (38.9

Mhz for all system).

Because of the internal VCO the IF circuit has a high immunity to EMC interferences.

QSS Sound circuit

The sound IF amplifier is similar to the vision IF amplifier

and has an external AGC decoupling capacitor.

The single reference QSS mixer is realised by

a multiplier. In this multiplier the SIF signal is converted

to the intercarrier frequency by

mixing it with the regenerated picture carrier from the VCO. The mixer

output signal is supplied to the output via a high-pass filter for attenuation of the residual video signals.

With this system a high performance hi-fi stereo sound processing can be achieved.

Video switches

The video switch has one input for an external CVBS or Y/C signal. The selected CVBS signal can be

supplied to pin 38, the IF video output. The selection between both signals is realised by the controlling

software in subaddress 22H.

The video ident circuit is connected to the selected signal. This ident circuit is independent of the

synchronisation.

Synchronisation circuit

The IC contains separator circuits for the horizontal and vertical sync pulses and a data-slicing circuit

which extracts the digital teletext data from the analogue signal.

The horizontal drive signal is obtained from an internal VCO which is running at a frequency of 25

MHz. This oscillator is stabilised to this frequency by using a 12 MHz signal coming from the

reference oscillator of the

µ

-Controller/Teletext decoder.

The horizontal drive is switched on and off via the soft start/stop procedure. This function is realised

by means of variation of the TON of the horizontal drive pulses.

The vertical synchronisation is realised by means of a divider circuit. The vertical ramp generator needs

an external resistor and capacitor. For the vertical drive a differential output current is available. The

outputs are DC coupled to the vertical output stage.

Содержание DTE-21U6TH

Страница 15: ...Service manual CP 785AF A 14...

Страница 18: ...Service manual CP 785AF 17...

Страница 30: ...Service manual CP 785AF 29 5 Circuit description 5 1 Block diagram...

Страница 60: ...Service manual CP 785AF 59 7 Exploded view...

Страница 61: ...Service manual CP 785AF 60 8 PCB Layout...

Страница 62: ...S ervice manual CP 785AF 61 9 Circuit Diagram...