CY7C67200

Document #: 38-08014 Rev. *G

Page 12 of 78

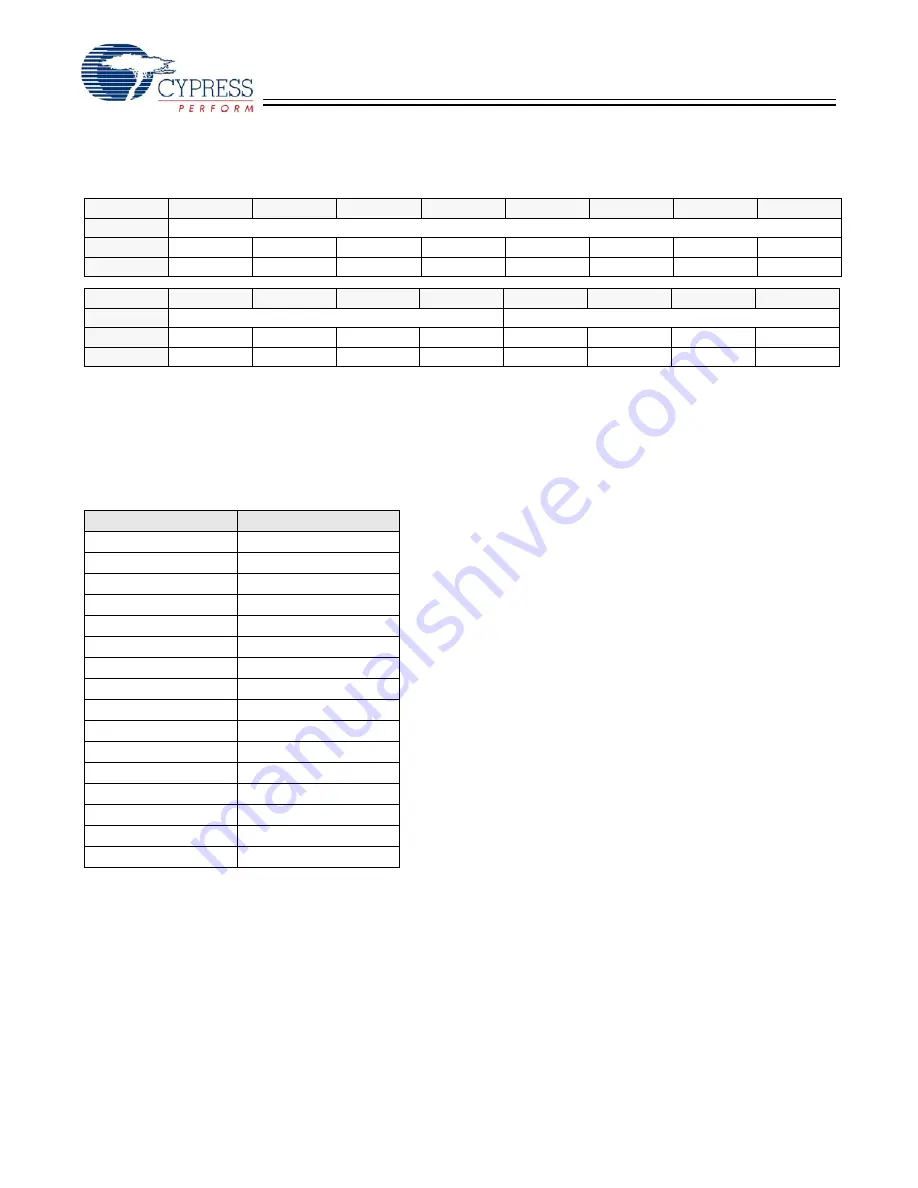

CPU Speed Register [0xC008] [R/W]

Figure 10. CPU Speed Register

Register Description

The CPU Speed register allows the processor to operate at a user selected speed. This register only affects the CPU; all other

peripheral timing is still based on the 48-MHz system clock (unless otherwise noted).

CPU Speed

(Bits[3:0])

The CPU Speed field is a divisor that selects the operating speed of the processor as defined in

Table 18

.

Reserved

All reserved bits must be written as ‘0’.

Bit #

15

14

13

12

11

10

9

8

Field

Reserved...

Read/Write

-

-

-

-

-

-

-

-

Default

0

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

...Reserved

CPU Speed

Read/Write

-

-

-

-

R/W

R/W

R/W

R/W

Default

0

0

0

0

1

1

1

1

Table 18.CPU Speed Definition

CPU Speed [3:0]

Processor Speed

0000

48 MHz/1

0001

48 MHz/2

0010

48 MHz/3

0011

48 MHz/4

0100

48 MHz/5

0101

48 MHz/6

0110

48 MHz/7

0111

48 MHz/8

1000

48 MHz/9

1001

48 MHz/10

1010

48 MHz/11

1011

48 MHz/12

1100

48 MHz/13

1101

48 MHz/14

1110

48 MHz/15

1111

48 MHz/16

[+] Feedback