WM8940

18

Rev 4.4

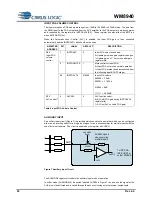

CONTROL INTERFACE TIMING

–

2-WIRE MODE

SDIN

SCLK

t

3

t

1

t

6

t

2

t

7

t

5

t

4

t

3

t

8

t

9

Figure 5 Control Interface Timing

– 2-Wire Serial Control Mode

Test Conditions

DCVDD=1.8V, DBVDD=AVDD=SPKVDD=3.3V, DGND=AGND=SPKGND=0V, T

A

= +25

o

C, Slave Mode, fs = 48kHz, MCLK =

256fs, 24-bit data, unless otherwise stated.

PARAMETER

SYMBOL

MIN

TYP

MAX

UNIT

Program Register Input Information

SCLK Frequency

0

526

kHz

SCLK Low Pulse-Width

t

1

1.3

us

SCLK High Pulse-Width

t

2

600

ns

Hold Time (Start Condition)

t

3

600

ns

Setup Time (Start Condition)

t

4

600

ns

Data Setup Time

t

5

100

ns

SDIN, SCLK Rise Time

t

6

300

ns

SDIN, SCLK Fall Time

t

7

300

ns

Setup Time (Stop Condition)

t

8

600

ns

Data Hold Time

t

9

900

ns

Pulse width of spikes that will be suppressed

t

ps

0

5

ns