7

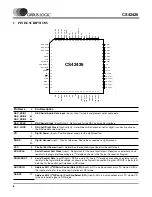

CS42426

INT

11

Interrupt

(Output) - The CS42426 will generate an interrupt condition as per the Interrupt Mask register.

See “Interrupts” on page 28 for more details.

RST

12

Reset

(

Input) - The device enters a low power mode and all internal registers are reset to their default

settings when low.

AINR-

AINR+

13

14

Differential Right Channel Analog Input

(

Input) - Signals are presented differentially to the delta-sigma

modulators via the AINR+/- pins.

AINL+

AINL-

15

16

Differential Left Channel Analog Input

(

Input) - Signals are presented differentially to the delta-sigma

modulators via the AINL+/- pins.

VQ

17

Quiescent Voltage

(

Output)

-

Filter connection for internal quiescent reference voltage.

FILT+

18

Positive Voltage Reference

(

Output) - Positive reference voltage for the internal sampling circuits.

REFGND

19

Reference Ground

(

Input) - Ground reference for the internal sampling circuits.

,-

,-

,-

,-

,-

,-

36,37

35,34

32,33

31,30

28,29

27,26

Differential Analog Output

(

Output) - The full-scale differential analog output level is specified in the

Analog Characteristics specification table.

VA

24

41

Analog Power

(

Input) - Positive power supply for the analog section.

AGND

25

40

Analog Ground

(

Input) - Ground reference. Should be connected to analog ground.

MUTEC

38

Mute Control

(

Output) - The Mute Control pin outputs high impedance following an initial power-on con-

dition or whenever the PDN bit is set to a ‘1’, forcing the codec into power-down mode. The signal will

remain in a high impedance state as long as the part is in power-down mode. The Mute Control pin goes

to the selected “active” state during reset, muting, or if the master clock to left/right clock frequency ratio

is incorrect. This pin is intended to be used as a control for external mute circuits to prevent the clicks

and pops that can occur in any single supply system. The use of external mute circuits are not manda-

tory but may be desired for designs requiring the absolute minimum in extraneous clicks and pops.

LPFLT

39

PLL Loop Filter

(

Output) - An RC network should be connected between this pin and ground.

GPO7

GPO6

GPO5

GPO4

GPO3

GPO2

GPO1

42

43

44

45

46

47

48

General Purpose Output

(

Output) - These pins can be configured as general purpose output pins, an

ADC overflow interrupt or Mute Control outputs according to the General Purpose Pin Control registers.

VLS

53

Serial Port Interface Power

(

Input) - Determines the required signal level for the serial port interfaces.

RMCK

55

Recovered Master Clock

(

Output) - Recovered master clock output from the External Clock Reference

(OMCK, pin 59) or the PLL which is locked to the incoming ADC_LRCK.

ADC_SDOUT

56

ADC Serial Data Output

(

Output) - Output for two’s complement serial audio PCM data from the output

of the internal and external ADCs.

ADCIN1

ADCIN2

58

57

External ADC Serial Input

(

Input) - The CS42426 provides for up to two external stereo analog to digital

converter inputs to provide a maximum of six channels on one serial data output line when the CS42426

is placed in One Line mode.

OMCK

59

External Reference Clock

(

Input) - External clock reference that must be within the ranges specified in

the register “OMCK Frequency (OMCK Freqx)” on page 38.

ADC_LRCK

60

ADC Left/Right Clock

(

Input/Output) - Determines which channel, Left or Right, is currently active on

the ADC serial audio data line.

ADC_SCLK

61

ADC Serial Clock

(Input/Output) - Serial clock for the ADC serial audio interface.