24

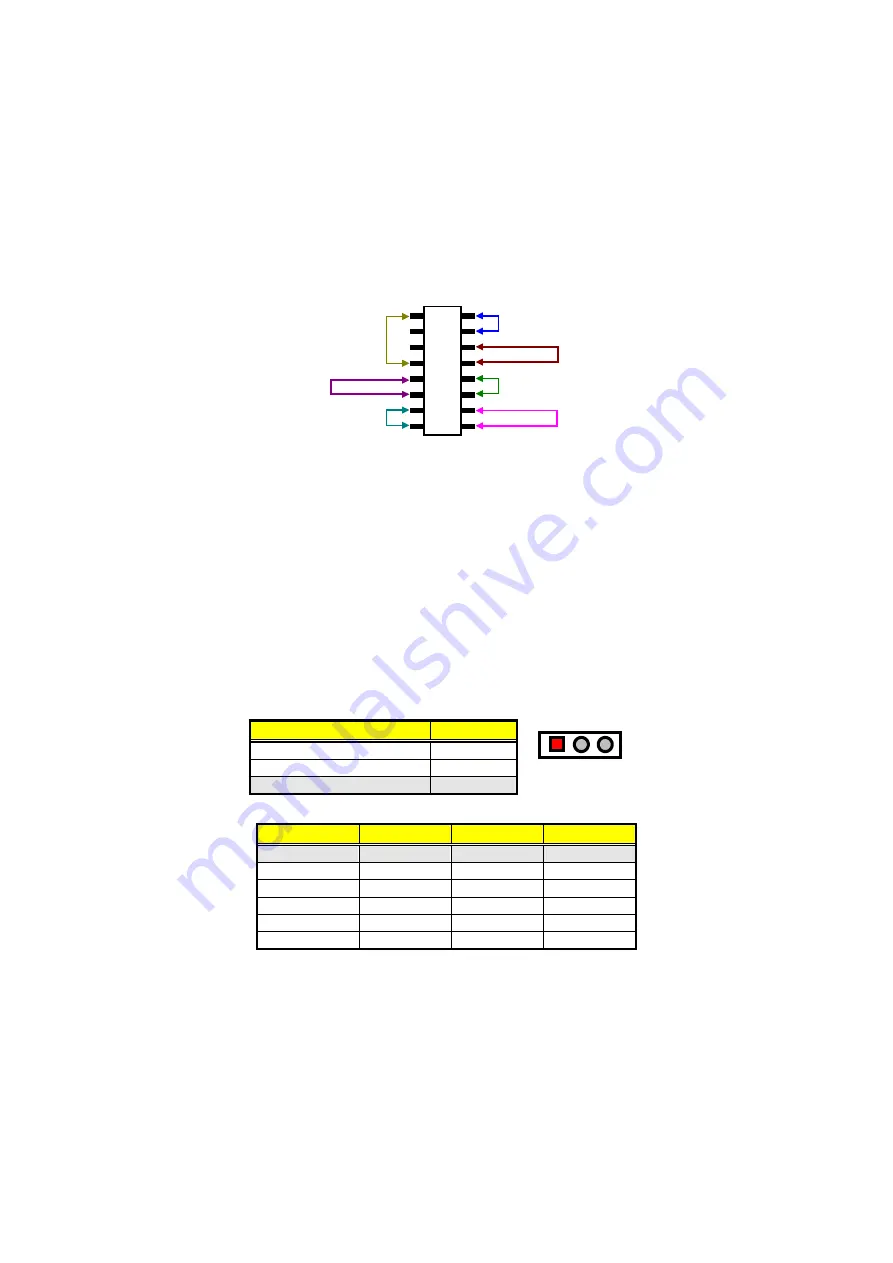

Connector JP3 Orientation

1

3

5

7

9

11

13

15

2

4

6

8

10

12

14

16

PWR LED

PWR button

SLP button

EXT_SMI

HD_LED

RST_SW

SPEAKER

3.20 Watchdog Timer

There are three access cycles of Watch-Dog Timer as Enable, Refresh

and Disable are the three access cycles of Watchdog Timer. The

Enable cycle proceeds via READ PORT 443H whereas the Disable

cycle proceeds via READ PORT 045H. A continued Enable cycle after

a first Enable cycle means Refresh.

Once the Enable cycle is active, a Refresh cycle is requested before

the time-out period. This restarts counting of the WDT period. When

the time counting goes over the period preset of WDT, it will assume

that the program operation is abnormal. A System Reset signal to

re-start or a NMI cycle to the CPU transpires when such error happens.

Jumper

JP1

is used to select the function of Watchdog Timer.

JP1

:

Watchdog Timer Active Type Setting

Options

Settings

Active NMI

Short 1-2

System Reset

Short 2-3

Disabled Watchdog Timer

Open

1

3

JP4(5-10): WDT Timeout Period Select

Period

PINS 5-6 PINS 7-8 PINS 9-10

1 sec

Short

Short

Short

2 sec

Open Short Short

10 sec

Short Open Short

20 sec

Open Open Short

110 sec

Short Short Open

220 sec

Open Short Open

Содержание HS-2604

Страница 6: ......

Страница 10: ...4 1 3 Board Dimensions ...

Страница 14: ...8 3 2 Board Layout ...

Страница 51: ...45 This page is intentionally left blank ...

Страница 58: ...52 2 Select the operating system of your computer to proceed with the installation process ...

Страница 64: ...58 2 Select on Other Devices from the list of devices then double click on PCI Ethernet Controller ...

Страница 79: ...73 This page is intentionally left blank ...