42

SAMA5D2 Xplained Ultra [USER GUIDE]

Atmel-44028B-ATARM-SAMA5D2-Xplained-Ultra-User Guide_02-Oct-15

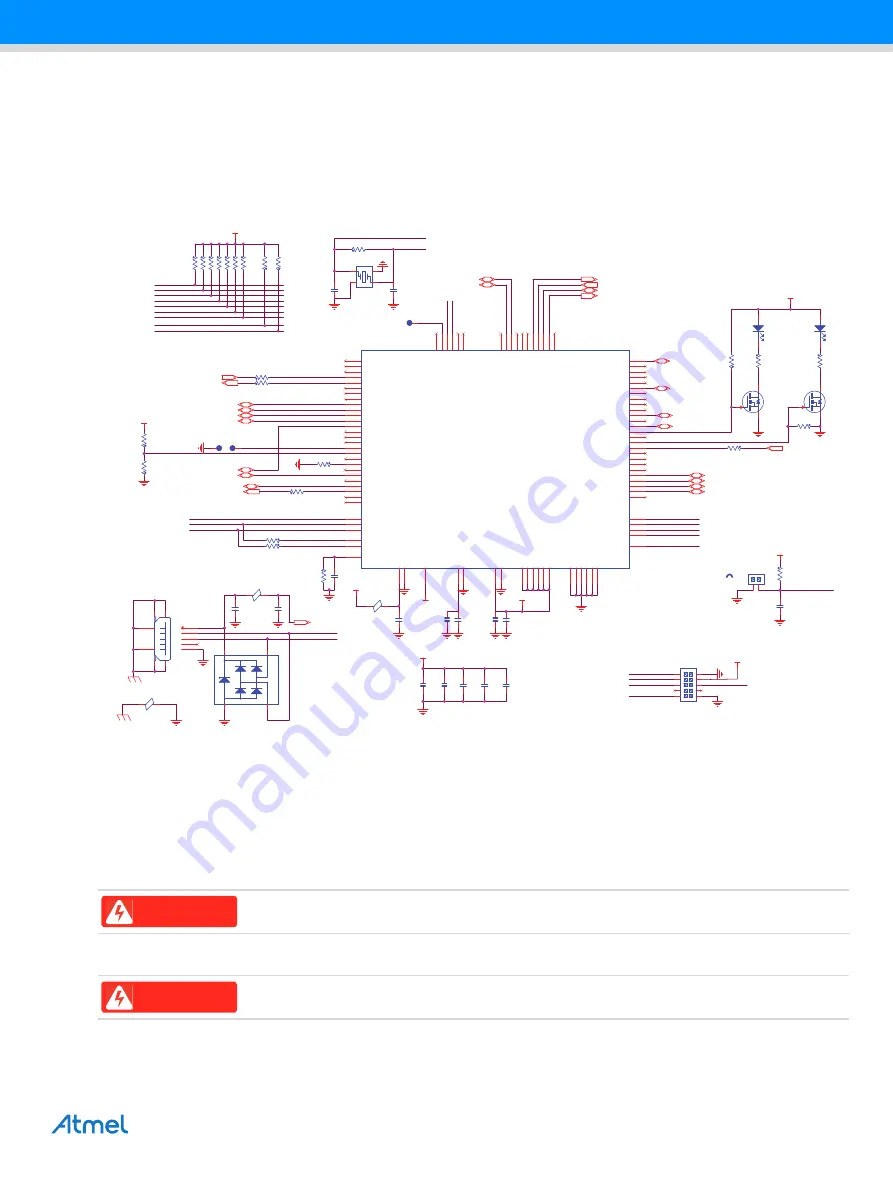

The EDBG is based on the Atmel AT32UC3A4256J high-performance low-power 32-bit AVR microcontroller

running at up to 60 MHz. The device includes an on-chip USB 2.0 high-speed hardware module with dedicated

DMA channels, making it ideal for data communications.

By default, the EDBG is in Reset state and not usable. To use the EDBG interface, remove the jumper JP1. To

avoid any conflicts with the debug signals, do not use the JTAG and EDBG at the same time.

Figure 5-41.

EDBG Interface

5.4.14 CDC Debug Interface

This feature is enabled only if pin J9 (RESET_N) of the microcontroller is not tied to ground. The pin is normally

pulled high and controlled by jumper JP1.

Jumper JP1 not installed: The CDC device is enabled.

Jumper JP1 installed: The CDC device is disabled.

EDBG_USB_HS_DP

EDBG_USB_HS_DM

EDBG_DGI_SDA

EDBG_DGI_SCL

EDBG

JTAG

(3V3)

EDBG_DIS

EDBG_TWI

Force s/n

EDBG_XIN

EDBG_XOUT

EDBG_USB_FS_DM

EDBG_USB_FS_DP

EDBG_USB_DM

EDBG_USB_VBUS_5V

EDBG_FORCE_BOOT

EDBG_CDC_UART_RX

EDBG_CDC_UART_TX

EDBG_XIN

EDBG_XOUT

STATUS_LED_CTRL

TARGET_RESET_SENSE

EDBG_JTAG_TCK

EDBG_JTAG_TDI

EDBG_JTAG_TDO

EDBG_JTAG_TMS

EDBG_RESET_N

EDBG_JTAG_TCK

EDBG_JTAG_TDO

EDBG_JTAG_TMS

EDBG_JTAG_TDI

EDBG_USB_DP

EDBG_USB_DP

EDBG_USB_DM

EDBG_ID_01

EDBG_ID_04

EDBG_ID_05

EDBG_ID_02

EDBG_ID_06

EDBG_ID_03

EDBG_RESET_N

EDBG_ADC0

EDBG_RESET_N

ERASE

EDBG_ID_07

EDBG_DGI_TWD

EDBG_DGI_TWCK

VDD_3V3

EARTH_USB_EDBG

EARTH_USB_EDBG

VSYS_5V

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

VDD_3V3

EDBG_DGI_TWD

[15]

EDBG_DGI_TWCK

[15]

EDBG_ID_01

[10]

DBGU_URXD1_PD2

[8,9]

DBGU_UTXD1_PD3

[8,9]

NRST

[4,9,10,12,14,15]

EDBG_SPI_MISO

[15]

EDBG_SPI_MOSI

[15]

EDBG_SPI_SCK

[15]

EDBG_SPI_NCS

[15]

EDBG_ID_04

[15]

EDBG_ID_05

[15]

EDBG_ID_06

[15]

EDBG_DGI_GPIO0

[15]

EDBG_DGI_GPIO1

[15]

EDBG_DGI_GPIO2

[15]

EDBG_DGI_GPIO3

[15]

EDBG_USB_VBUS_5V

[4]

EDBG_ID_02

[15]

EDBG_ID_03

[15]

EDBG_ID_07

[15]

NRST

[4,9,10,12,14,15]

EDBG_JTAG_TCK_PD14

[8]

EDBG_JTAG_TDI_PD15

[8]

EDBG_JTAG_TDO_PD16

[8]

EDBG_JTAG_TMS_PD17

[8]

R5

330R

R56

1

K

C9

10pF

R52

1

K

C175

100nF

R59

470R

R10

6.8K 1%

D3

BLUE

L13

180ohm at 100MHz

1

2

R54

1

K

TP4

SMD

VBUS

SHD

DM

DP

ID

GND

J14

MicroUSB AB Connector

1

2

3

4

5

8

6

11

7

9

10

C14

20pF

R55

1

K

R4

330R

C168

2.2uF

R2

200K

R331

2.2K

R51

1

K

D4

RED

R1

10K

C172

100nF

R3

100K

U1

AT32UC3A4256HHB-C1UR ( AT32UC3A4256J-C1UR, Factory Programmed )

PA00 / PA18

G8

PA01 / PA17

G10

PA02 / PX47

E1

PA03

F9

PA04

E9

PA05

G9

PA06 / PA13

E8

PA07 / PA19

H10

PA08

F8

PA10

C10

PA11

C9

PA12 / PA25

G7

PA14 / PX11

K7

PA15 / PX45

J7

PA16

E7

PA20 / PX18

H9

PA21 / PX22

K10

PA22 / PX20

H6

PA23 / PX46

G6

PA24 / PX17

J10

PA09

D8

PA26 / PB05

F7

PA27

A2

PA28

A1

PA29

B4

PA30

A4

PA31

C2

USB_VBUS

A10

DMHS

A9

DPHS

A8

DMFS

B9

DPFS

B8

USB_VBIAS

C7

VDDANA

J6

GNDANA

H8

VDDIN_1

D9

VDDCORE

E10

GNDCORE

F10

VDDIN_2

D10

GNDPLL

B10

VDDIO_1

E5

VDDIO_2

B5

VDDIO_3

J5

VDDIO_4

B6

VDDIO_5

F2

VDDIO_6

F6

GNDIO_1

F5

GNDIO_2

C3

GNDIO_3

H3

GNDIO_4

E2

GNDIO_5

C8

GNDIO_6

E6

PC00 / PX14

K5

PC01

K6

PC02

A5

PC03

A6

PC04

B7

PC05

A7

PB00

B1

PB01

B2

PB02

B3

PB03

C4

PB04

A3

PB06

D7

PB07

D6

PB08

C6

PB09

C5

PB10

D5

PB11

C1

PX00

G4

PX01

G2

PX02

G3

PX03

J1

PX04

H1

PX05

G1

PX06

F3

PX07

F4

PX08

E3

PX09

E4

PX10

D2

PX12

D1

PX13

D3

PX15 / PX32

K4

PX16 / PX53

D4

PX19 / PX59

F1

PX21

H2

PX23

K1

PX24

J2

PX25

H4

PX26

J3

PX27

K2

PX28

K3

PX29

J4

PX30

G5

PX31

H5

RESET_N

J9

TMS

H7

TDO

J8

TDI

K8

TCK

K9

R46

330R

R25

39R

Y1

12MHz CL=15pF

1

4

3

2

JPR1

Jumper

R43

100K

R23

39R

R57

1

K

R58

1

K

C49

1nF

L4

180ohm at 100MHz

1

2

C179

2.2uF

C174

100nF

C50

1nF

Q4

BSS138

1

3

2

GND

VCC

IO1

IO2

U5

PRTR5V0U2X

1

2

3

4

J10

DNP(Header 2X5)

1

2

3

4

5

6

7

8

9

10

C11

20pF

C5

1nF

L11

180ohm at 100MHz

1

2

R50

0R

JP1

Header 1X2

1

2

C178

100nF

R63

470R

TP2

SMD

TP1

SMD

C171

2.2uF

R29

DNP(1M)

R334

2.2K

C6

2.2uF

Q5

BSS138

1

3

2

R329

0R

R53

100K

C4

100nF

C15

100nF

WARNING

The default baud rate CDC is 57600 (57600/N/8/1).

WARNING

When using a console with the EDBG-CDC, the jumper JP2 DEBUG_DIS should be

ON.