628

32072H–AVR32–10/2012

AT32UC3A3

27.5

I/O Lines Description

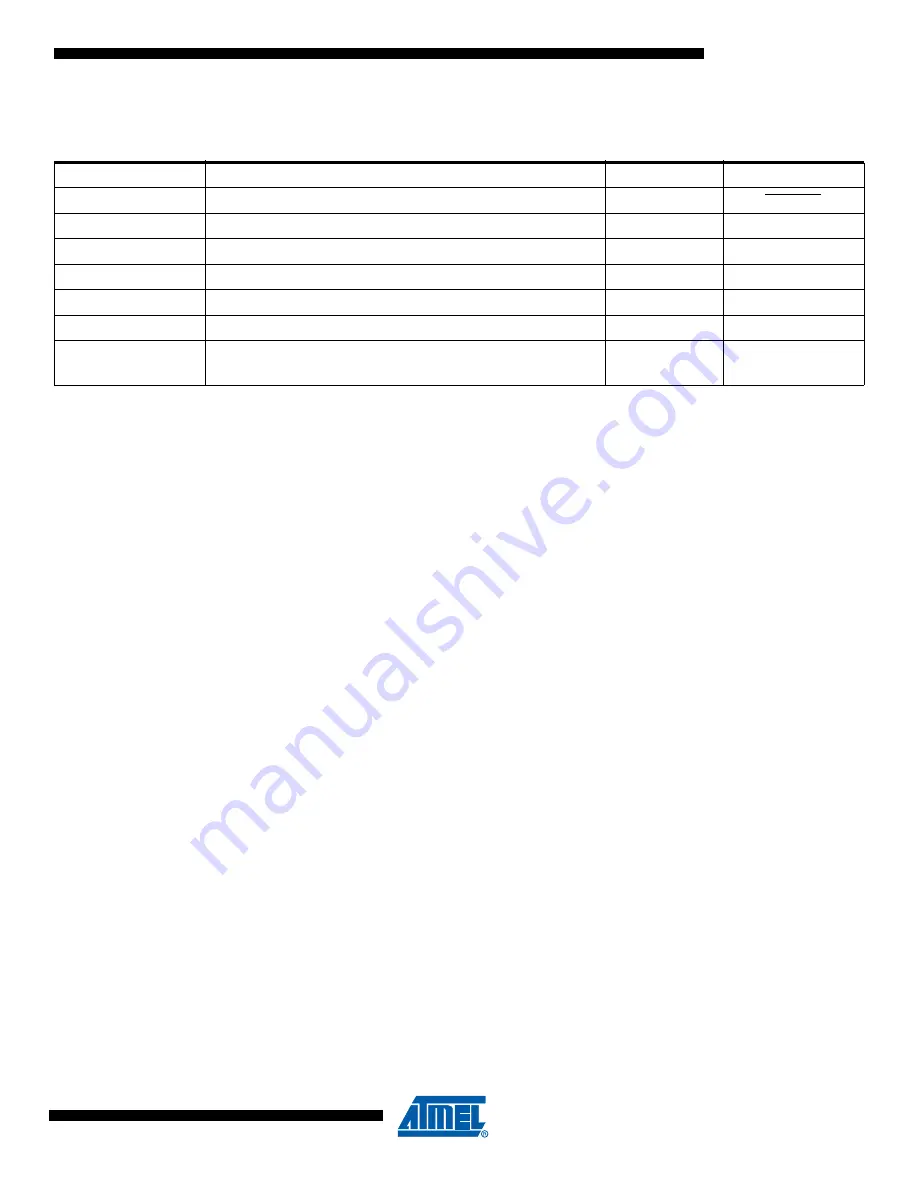

Table 27-3.

I/O Lines Description

PIn Name

Pin Description

Type

Active Level

USB_VBOF

USB VBus On/Off: Bus Power Control Port

Output

VBUSPO

USB_VBUS

VBus: Bus Power Measurement Port

Input

DMFS

FS Data -: Full-Speed Differential Data Line - Port

Input/Output

DPFS

FS Data +: Full-Speed Differential Data Line + Port

Input/Output

DMHS

HS Data -: Hi-Speed Differential Data Line - Port

Input/Output

DPHS

HS Data +: Hi-Speed Differential Data Line + Port

Input/Output

USB_ID

USB Identification: Mini Connector Identification Port

Input

Low: Mini-A plug

High Z: Mini-B plug

Содержание AT32UC3A3128

Страница 61: ...61 32072H AVR32 10 2012 AT32UC3A3 PLLEN PLL Enable 0 PLL is disabled 1 PLL is enabled...

Страница 260: ...260 32072H AVR32 10 2012 AT32UC3A3 5 2560 3071 6 3072 3583 7 3584 4095 Bit Index n Sector Boundaries...

Страница 592: ...592 32072H AVR32 10 2012 AT32UC3A3 Manchester Configuration Register on page 614...

Страница 989: ...989 32072H AVR32 10 2012 AT32UC3A3 37 2 Package Drawings Figure 37 1 TFBGA 144 package drawing...

Страница 991: ...991 32072H AVR32 10 2012 AT32UC3A3 Figure 37 3 VFBGA 100 package drawing...