On-Card SDRAM

4-5

ration register 8 (F0

16

) have been carefully tuned for optimum memory cycle

times for 100-MHz SDRAMs (running at 83MHz in the current configuration)

under a variety of conditions.

The table below describes the wait states for the BajaPPC-750.

For non-burst cycles, the number in the “Total Clocks” column of Table 4-4 is the

total number of CPU clock cycles required to complete the transfer, and the num-

ber in the “Wait States” column is the number of wait states per cycle.

For burst cycles, the number in the “Total Clocks” column of Table 4-4 is the total

number of CPU clocks for the first access of the four 8-word (64-bit) burst, plus

the number of clocks for the second, third, and fourth cycles. The number in the

“Wait States” column is the number of wait states for each of the four accesses.

There are two other sources of wait states that SDRAM architectures can exhibit:

•

When a refresh must be performed and the SDRAM controller is unable to

perform the refresh during non-RAM cycles. This happens so infrequently

that any performance degradation is usually unnoticeable.

•

When the processor is required to perform back-to-back memory cycles with

no delays. This is also rare because of the instruction cache. In the event of a

back-to-back memory cycle, an additional two-clock-cycle wait is inserted

between accesses.

While the above information is important in comparing the relative performance

of SDRAM designs, the performance of individual SDRAM designs has much less

impact on overall system performance than one might expect. The reason for this

is that the internal instruction and data cache built into the CPU helps to decou-

ple the processor from slower speed memories such as SDRAMs.

To summarize, the higher the cache hit rates, the less impact external memory

has on system performance.

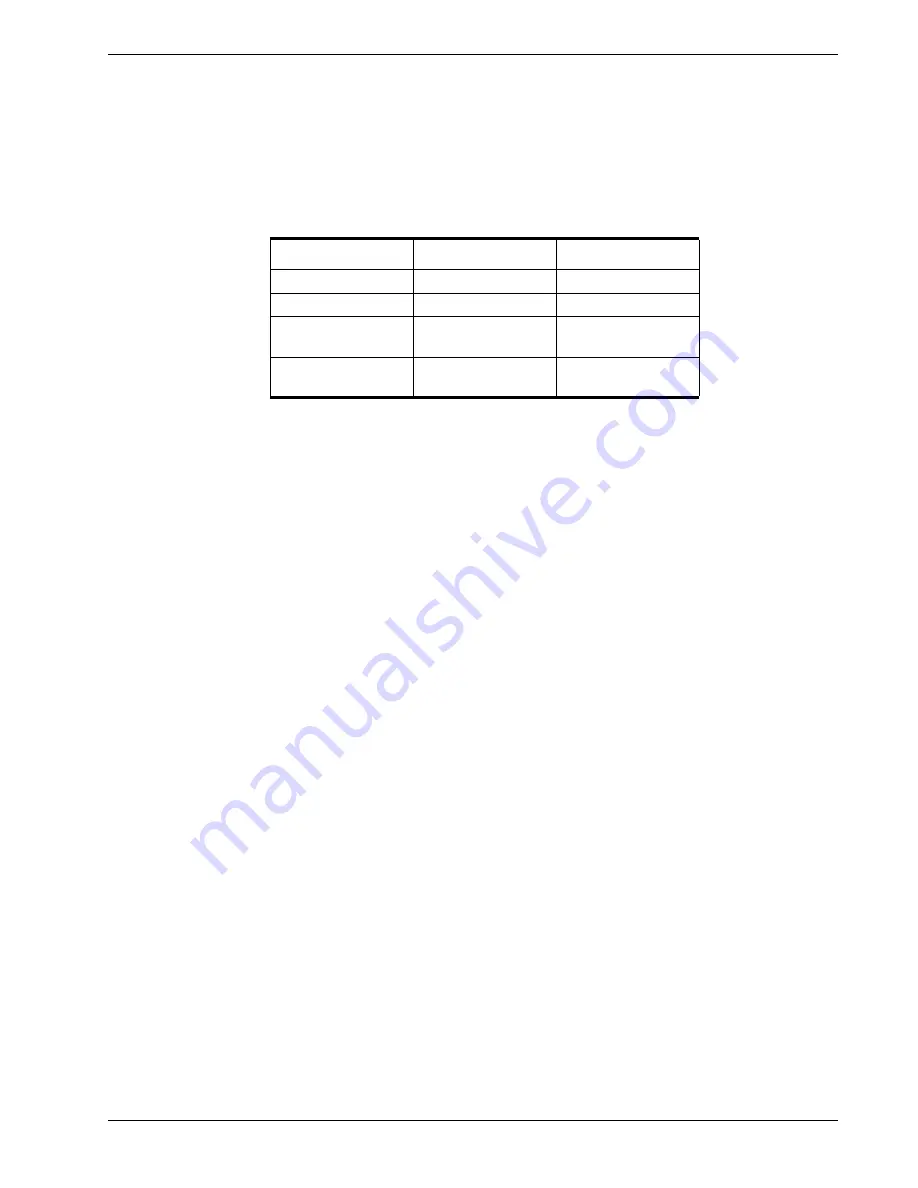

Table 4-4. SDRAM Access Time Required for the BajaPPC-750

Cycle

Total Clocks

Wait States

Reads

7

6

Writes

3

2

Burst Read

(4 accesses)

7-1-1-1

6-0-0-0

Burst Write

(4 accesses)

3-1-1-1

2-0-0-0

Содержание BajaPPC-750

Страница 2: ...BajaPPC 750 PowerPC Based Single Board Computer User s Manual May 2002...

Страница 4: ...BajaPPC 750 PowerPC Based Single Board Computer User s Manual May 2002...

Страница 7: ......

Страница 16: ...0002M621 15 ix Register Map 9 1 Counter Timer Status CTSR 9 2 Register Map 9 2 Counter Timer Mode CTMR 9 4...

Страница 19: ...xii BajaPPC 750 Contents...

Страница 57: ...3 12 BajaPPC 750 Central Processing Unit May 2002...

Страница 77: ...5 12 BajaPPC 750 PMC PCI Interface May 2002...

Страница 111: ...6 34 BajaPPC 750 VMEbus Interface May 2002...

Страница 135: ...8 18 BajaPPC 750 Serial and Parallel I O May 2002...

Страница 207: ...10 68 BajaPPC 750 Monitor May 2002...