Bus Interface Unit

ARM DDI 0186A

Copyright © 2000 ARM Limited. All rights reserved.

6-17

6.4

AHB clocking

The ARM966E-S design uses a single rising edge clock

CLK

to time all internal

activity. In many systems where the ARM966E-S is embedded, it is desirable to run the

AHB at a lower rate. To support this requirement, the ARM966E-S requires a clock

enable,

HCLKEN

, to time AHB transfers.

The

HCLKEN

input is driven HIGH around a rising edge of the ARM966E-S

CLK

to

indicate that this rising edge is also a rising edge of

HCLK

. This requires that

HCLK

is synchronous to the ARM966E-S

CLK

.

When the ARM9E-S is running from tightly-coupled SRAM or performing writes using

the write buffer, the ARM966E-S

HCLKEN

and

HREADY

inputs are ignored in terms

of generating the

SYSCLKEN

core stall signal. The core is only stalled by SRAM stall

cycles or if the write buffer overflows. This means that the ARM9E-S is executing

instructions at the faster

CLK

rate and is effectively decoupled from the

HCLK

domain

AHB system.

If however, an AHB read access or unbuffered write is required, the core is stalled until

the AHB transfer has completed. Because the AHB system is being clocked by the

lower rate

HCLK

, it is necessary to examine

HCLKEN

to detect when to drive out the

AHB address and control to start an AHB transfer.

HCLKEN

is then required to detect

the following rising edges of

HCLK

so that the BIU knows the access has completed.

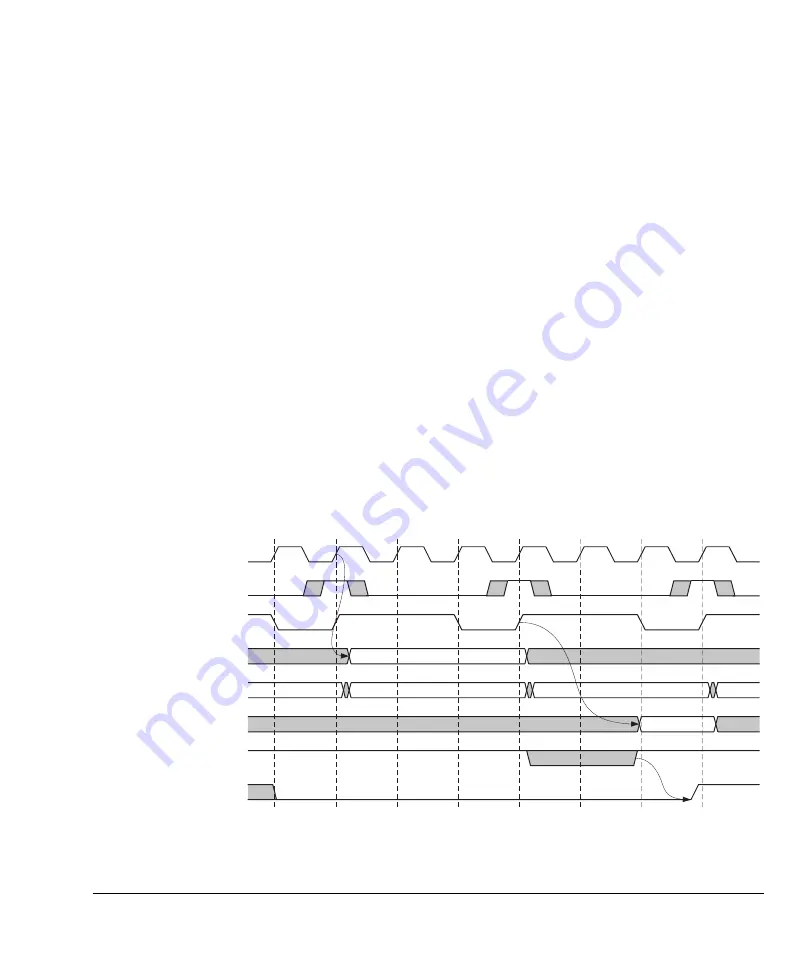

Figure 6-13 shows an example of an AHB read access where there is a 3:1 ratio of

CLK

to

HCLK

.

Figure 6-13 AHB 3:1 clocking example

CLK

HCLKEN

HADDR[31:0]

HREADY

HTRANS

HRDATA[31:0]

HCLK

Addr A

NONSEQ

IDLE

IDLE

Read data (A)

SYSCLKEN

Содержание ARM966E-S

Страница 6: ...Contents vi Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 20: ...Introduction 1 4 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 48: ...Tightly coupled SRAM 4 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 80: ...Bus Interface Unit 6 20 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 118: ...Debug Support 8 26 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 130: ...Test Support 10 8 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 142: ...Instruction cycle timings 11 12 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 158: ...Signal Descriptions A 16 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...

Страница 176: ...AC Parameters B 18 Copyright 2000 ARM Limited All rights reserved ARM DDI 0186A ...