Bus Interface Unit and Write Buffer

6-10

Copyright © ARM Limited 2000. All rights reserved.

relative to HCLK but are sampled within the ARM946E-S with CLK. This leads to

hold time issues, from CLK to HCLK on outputs, and from HCLK to CLK on inputs.

In order to minimize this effect you must minimize the skew between HCLK and CLK.

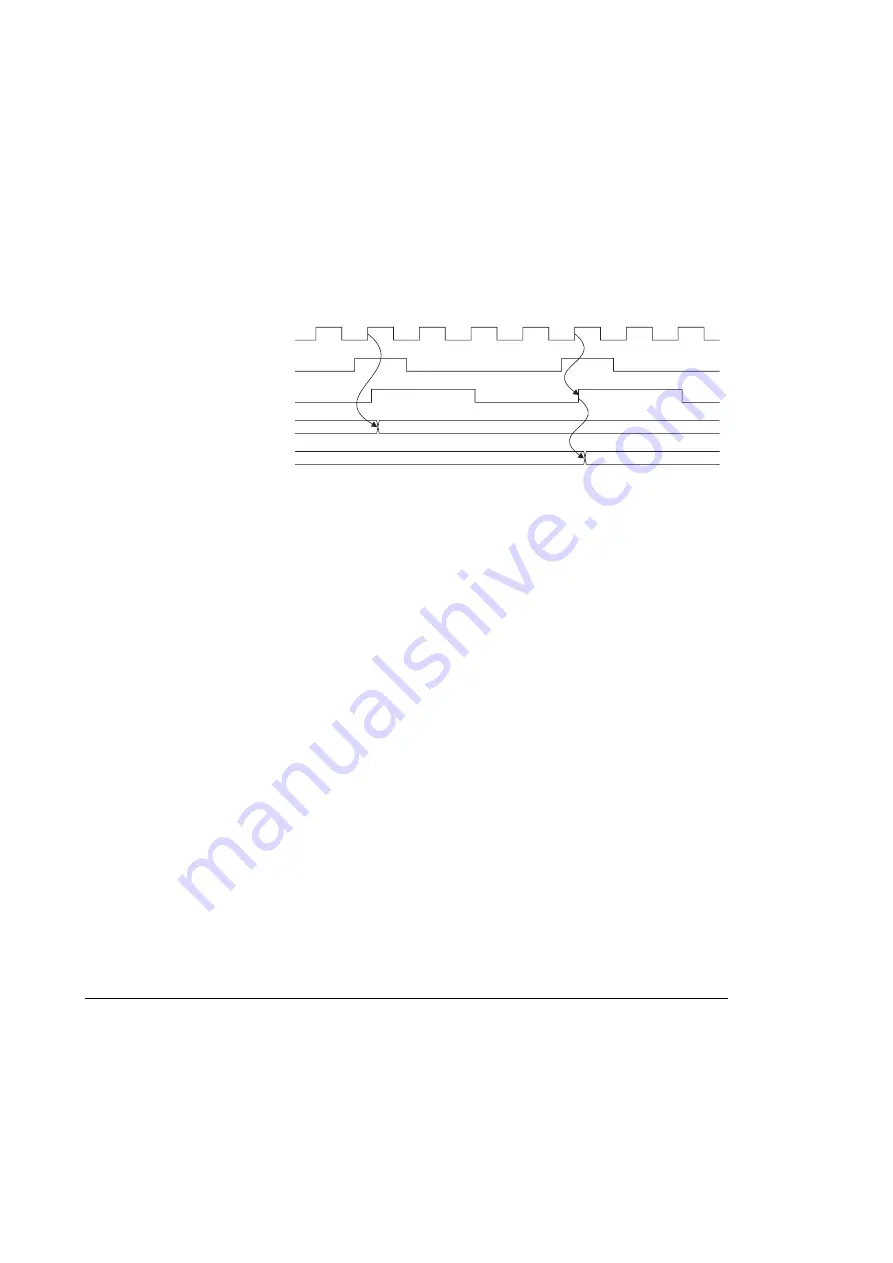

Figure 6-6 shows the AHB clock relationships.

Figure 6-6 AHB clock relationships

Clock tree insertion at top level

Considering the skew issue in more detail, the ARM946E-S requires a clock tree to be

inserted to allow an evenly distributed clock to be driven to all the registers in the

design. The registers that drive out AHB outputs and sample AHB inputs are therefore

timed off CLK at the bottom of the inserted clock tree and subject to the clock tree

insertion delay. To maximize performance, when the ARM946E-S is embedded in an

AHB system, the clock generation logic to produce HCLK must be constrained so that

it matches the insertion delay of the clock tree within the ARM946E-S. You can achieve

this using a clock tree insertion tool, if the clock tree is inserted for the ARM946E-S

and the embedded system at the same time (top level insertion).

CLK

HCLK

HCLKEN

AHB outputs

from ARM946E-S

AHB inputs

to ARM946E-S

Skew between

and

CLK

HCLK

Содержание ARM946E-S

Страница 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Страница 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Страница 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 98: ...Bus Interface Unit and Write Buffer 6 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...