Debug Support

Copyright © ARM Limited 2000. All rights reserved.

8-7

8.3

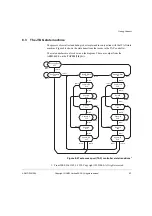

The JTAG state machine

The process of serial test and debug is best explained in conjunction with the JTAG state

machine. Figure 8-4 shows the state transitions that occur in the TAP controller.

The state numbers are also shown on the diagram. These are output from the

ARM946E-S on the TAPSM[3:0] bits.

Figure 8-4 Test access port (TAP) controller state transitions

1

Select-DR-Scan

0x7

Capture-DR

0x6

Shift-DR

0x2

Exit1-DR

0x1

Pause-DR

0x3

Exit2-DR

0x0

Update-DR

0x5

Run-Test/Idle

0xC

Test-Logic-Reset

0xF

tms=0

tms=0

tms=1

tms=0

tms=1

tms=1

Select-IR-Scan

0x4

Capture-IR

0xE

Shift-IR

0xA

Exit1-IR

0x9

Pause-IR

0xB

Exit2-IR

0x8

Update-IR

0xD

tms=0

tms=0

tms=1

tms=0

tms=1

tms=1

tms=0

tms=0

tms=0

tms=0

tms=1

tms=0

tms=1

tms=0

tms=1

tms=1

tms=0

tms=1

tms=1

tms=1

tms=0

tms=1

tms=0

tms=1

tms=1

tms=0

1. From IEEE Std 1149.1-1990. Copyright 1999IEEE. All rights reserved.

Содержание ARM946E-S

Страница 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Страница 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Страница 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 98: ...Bus Interface Unit and Write Buffer 6 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Страница 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...