EVAL-AD7403FMCZ User Guide

UG-683

Rev. 0 | Page 9 of 20

LINK CONFIGURATION OPTIONS

There are multiple link options that must be set correctly to

select the appropriate operating setup before you begin using

the evaluation board. The functions of these options are

outlined in Table 2.

SETUP CONDITIONS

Care should be taken before

applying power and signals to the

evaluation board to ensure that all link positions are as required

by the operating mode. There are two modes in which to operate

the evaluation board. The evaluation board can be operated in

SDP-H1 controlled mode to be used with the the

EVAL-SDP-CH1Z

board, or the evaluation board can be used in standalone mode.

The Default Position column of Table 2 shows the default

positions in which the links are set when the evaluation board is

packaged. When the board is shipped, it is set up to operate in

SDP-H1 controlled mode, with the power supplied from the

EVAL-SDP-CH1Z

board and the analog supply rail (V

DD1

) being

supplied via the on-board

iso

Power®

ADuM6000

dc-to-dc converter.

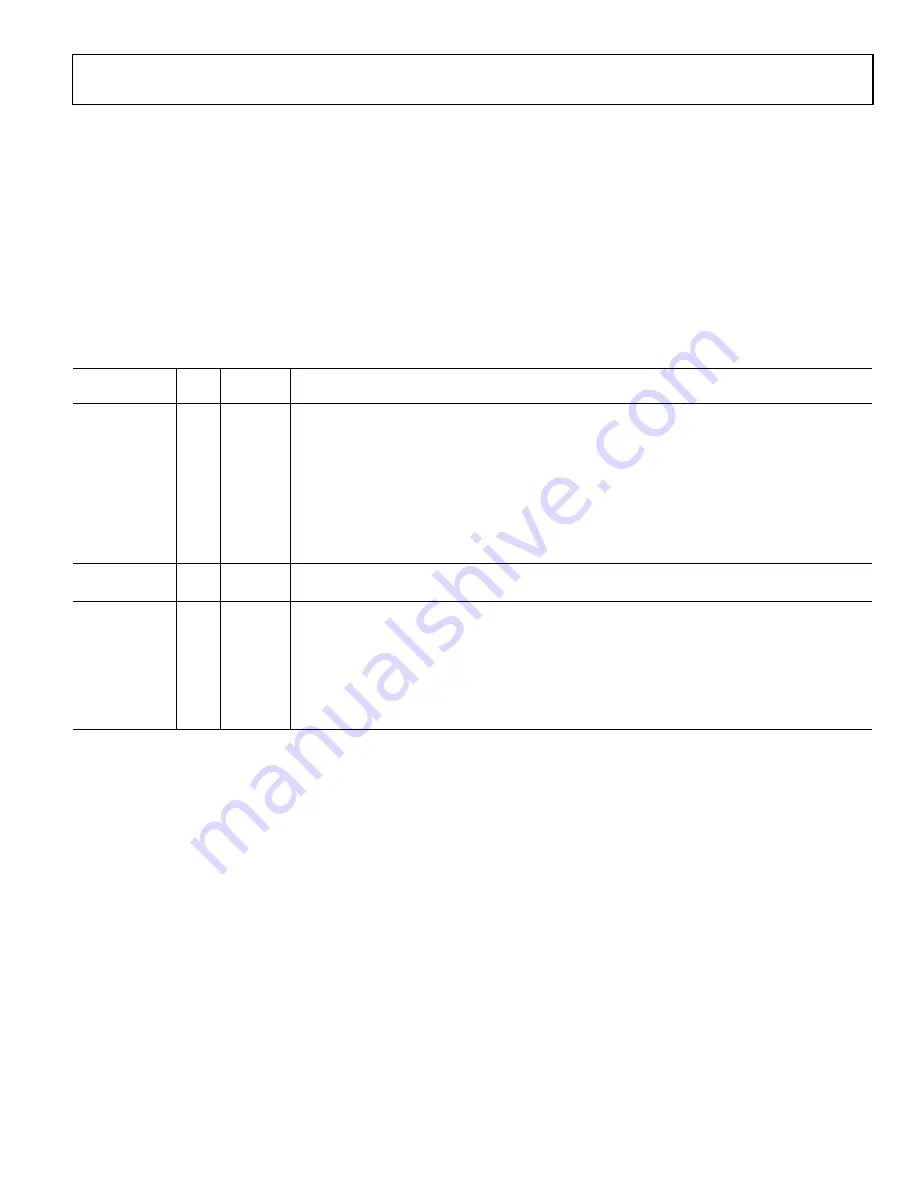

Table 2. Link Options

Category

Link

Default

Position

Function

Power Supplies LK1

A

This link selects the

AD7403

V

DD1

supply source. Remove LK5 if using either Position A or Position B.

Position A: V

DD1

is supplied from the

ADuM6000

on-board device.

Position B: V

DD1

is supplied externally via Connector J5.

LK5

Removed When LK5 is inserted, V

DD1

is supplied via a step-down dc-to-dc regulator via J7. Remove LK5 if V

DD1

is

supplied via LK1.

LK2

A

This link selects the

AD7403

V

DD2

supply source.

Position A: V

DD2

is supplied from the

EVAL-SDP-CH1Z

board.

Position B: V

DD2

is supplied from the on-board 5 V regulator.

Position C: V

DD2

is supplied externally via Connector J6.

Analog Input

LK7

Removed When LK7 is inserted, AIN+ is shorted to ground. Remove LK7 if a signal is applied to AIN+.

LK8

Inserted

When LK8 is inserted, AIN− is shorted to ground. Remove LK8 if a signal is applied to AIN−.

Serial Interface

LK3

A

This link is used to select the MCLK source for the serial interface.

Position A: MCLK is sourced from the

EVAL-SDP-CH1Z

board.

Position B: Do not use.

Position C: MCLK is sourced from the J3 SMB jack. (Standalone mode.)

LK4

A

This link is used to route the MDAT output for the serial interface.

Position A: MDAT is sent to the

EVAL-SDP-CH1Z

board.

Position B: MDAT is sent to the J4 SMB jack. (Standalone mode.)