ADV8003 Hardware Manual

Rev. B, August 2013

136

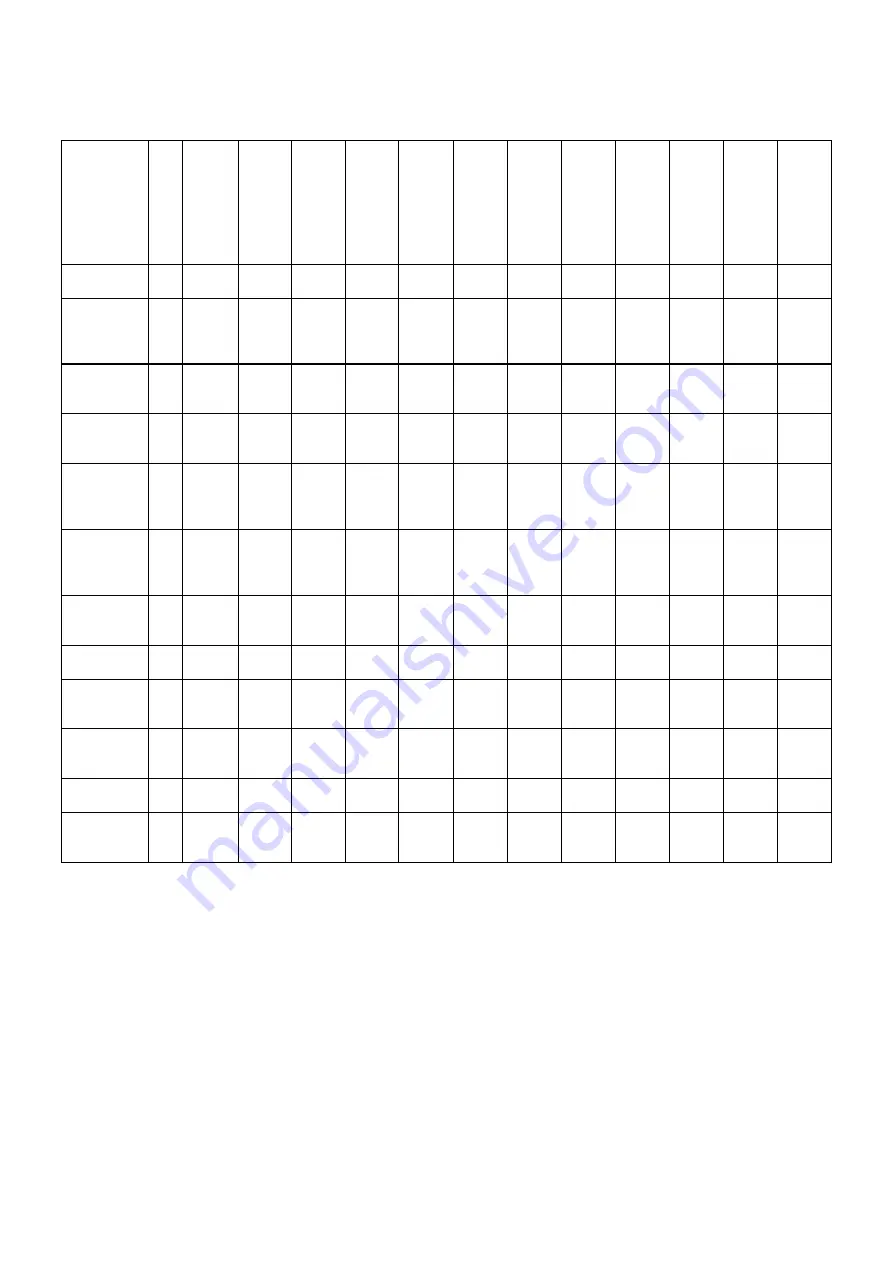

Color Space

Conversion

cs

c_

m

od

e[1

:0

]

A1

A2

A3

A4

B1

B2

B3

B4

C1

C2

C3

C4

HDTV YCbCr

(limited)

SDTV YCbCr

(limited) to

SDTV YCbCr

(full)

0x1 0x091B 0x0000 0x0000 0x1F6E 0x0000 0x0950 0x0000 0x1F6B 0x0000 0x0000 0x091B 0x1F6E

SDTV YCbCr

(limited) to

RGB (limited)

0x1 0x0AF8 0x0800 0x0000 0x1A84 0x1A6A 0x0800 0x1D50 0x0423 0x1FFC 0x0800 0x0DDE 0x1913

SDTV YCbCr

(limited) to

RGB (full)

0x2 0x0669 0x04AC 0x0000 0x1C81 0x1CBC 0x04AD 0x1E6E 0x0220 0x1FFE 0x04AD 0x081A 0x1BA9

SDTV YCbCr

(full) to HDTV

YCbCr

(limited)

0x2 0x039D 0x0000 0x0043 0x0F26 0x1F44 0x036F 0x1F97 0x00D2 0x0067 0x0000 0x0397 0x004D

RGB (limited)

to HDTV

YCbCr

(limited)

0x0 0x082E 0x1893 0x1F3F 0x0800 0x0367 0x0B71 0x0128 0x0000 0x1E21 0x19B2 0x082D 0x0800

RGB (limited)

to SDTV YCbCr

(limited)

0x0 0x082E 0x1926 0x1EAC 0x0800 0x04C9 0x0965 0x01D2 0x0000 0x1D3F 0x1A93 0x082E 0x0800

RGB (limited)

to RGB (full)

0x0 0x0DBC 0x0000 0x0000 0x0100 0x0000 0x0DBC 0x0000 0x0100 0x0000 0x0000 0x0DBC 0x0100

RGB (full) to

HDTV YCbCr

(limited)

0x0 0x06FF 0x19A6 0x1F5B 0x0800 0x02E9 0x09CB 0x00FD 0x0100 0x1E66 0x1A9B 0x06FF 0x0800

RGB (full) to

SDTV YCbCr

(limited)

0x0 0x06FF 0x1A24 0x1EDD 0x0800 0x0418 0x080A 0x018F 0x0100 0x1DA5 0x1B5C 0x06FF 0x0800

RGB (full) to

RGB (limited)

0x1 0x0950 0x0000 0x0000 0x1F6B 0x0000 0x0950 0x0000 0x1F6B 0x0000 0x0000 0x0950 0x1F6B

Identity Matrix

(Output =

Input)

0x1 0x0800 0x0000 0x0000 0x0000 0x0000 0x0800 0x0000 0x0000 0x0000 0x0000 0x0800 0x0000

2.2.12.3.

RX Input Channel CSC

The CSC must be manually configured for each color space conversion. The CSC on the RX input channel can be enabled using the

control. The CSC mode on the RX input channel can be configured using

. The CSC mode is used to

define the fixed point position of the CSC coefficients which are located after

in the IO Map for the RX input channel.

Reference configuration scripts to configure the RX input channel CSC are provided with the evaluation software.

rx_csc_enable

, IO Map,

Address 0x1B70[7]

This bit is used to enable the RX input channel CSC.

Содержание ADV8003

Страница 364: ...ADV8003 Hardware Manual Rev B August 2013 364 s HPD HEAC CL DA C_GND 5V G_DET Figure 142 ADV8003 Schematic Page 2...

Страница 365: ...ADV8003 Hardware Manual Rev B August 2013 365 Figure 143 ADV8003 Schematic Page 3 Date August 2011 Rev 0...

Страница 366: ...ADV8003 Hardware Manual Rev B August 2013 366 Figure 144 ADV8003 Schematic Page 4...

Страница 367: ...ADV8003 Hardware Manual Rev B August 2013 367 Figure 145 ADV8003 Schematic Page 5...

Страница 368: ...ADV8003 Hardware Manual Rev B August 2013 368 Figure 146 ADV8003 Schematic Page 6...

Страница 369: ...ADV8003 Hardware Manual Rev B August 2013 369 Figure 147 ADV8003 Schematic Page 7...

Страница 370: ...ADV8003 Hardware Manual Rev B August 2013 370 Figure 148 ADV8003 Schematic Page 8 Date August 2011 Rev 0...

Страница 371: ...ADV8003 Hardware Manual Rev B August 2013 371 Figure 149 ADV8003 Schematic Page 9...

Страница 372: ...ADV8003 Hardware Manual Rev B August 2013 372 Figure 150 ADV8003 Schematic Page 10...

Страница 373: ...ADV8003 Hardware Manual Rev B August 2013 373 Figure 151 ADV8003 Schematic Page 11...

Страница 374: ...ADV8003 Hardware Manual Rev B August 2013 374 Figure 152 ADV8003 Schematic Page 12...

Страница 375: ...ADV8003 Hardware Manual Rev B August 2013 375 Figure 153 ADV8003 Schematic Page 13...

Страница 376: ...ADV8003 Hardware Manual Rev B August 2013 376 Figure 154 ADV8003 Schematic Page 14...

Страница 377: ...ADV8003 Hardware Manual Rev B August 2013 377 Figure 155 ADV8003 Schematic Page 15...

Страница 378: ...ADV8003 Hardware Manual Rev B August 2013 378 Figure 156 ADV8003 Schematic Page 16...

Страница 379: ...ADV8003 Hardware Manual Rev B August 2013 379 Figure 157 ADV8003 Schematic Page 17...

Страница 380: ...ADV8003 Hardware Manual Rev B August 2013 380 Figure 158 ADV8003 Schematic Page 18...

Страница 381: ...ADV8003 Hardware Manual Rev B August 2013 381 Figure 159 ADV8003 Schematic Page 19...

Страница 382: ...ADV8003 Hardware Manual Rev B August 2013 382 Figure 160 ADV8003 Schematic Page 20...

Страница 383: ...ADV8003 Hardware Manual Rev B August 2013 383 Figure 161 ADV8003 Schematic Page 21...

Страница 384: ...ADV8003 Hardware Manual Rev B August 2013 384 Figure 162 ADV8003 Schematic Page 22...

Страница 385: ...ADV8003 Hardware Manual Rev B August 2013 385 Figure 163 ADV8003 Schematic Page 23...

Страница 386: ...ADV8003 Hardware Manual Rev B August 2013 386 Figure 164 ADV8003 Schematic Page 24...

Страница 387: ...ADV8003 Hardware Manual Rev B August 2013 387 Figure 165 ADV8003 Schematic Page 25...

Страница 388: ...ADV8003 Hardware Manual Rev B August 2013 388 Figure 166 ADV8003 Schematic Page 26...

Страница 389: ...ADV8003 Hardware Manual Rev B August 2013 389 Figure 167 ADV8003 Schematic Page 27...

Страница 390: ...ADV8003 Hardware Manual Rev B August 2013 390 Figure 168 ADV8003 Schematic Page 28...

Страница 391: ...ADV8003 Hardware Manual Rev B August 2013 391 Figure 169 ADV8003 Schematic Page 29...

Страница 392: ...ADV8003 Hardware Manual Rev B August 2013 392 Figure 170 ADV8003 Schematic Page 30...

Страница 393: ...ADV8003 Hardware Manual Rev B August 2013 393 Figure 171 ADV8003 Schematic Page 31...

Страница 395: ...ADV8003 Hardware Manual Rev B August 2013 395 Figure 173 ADV8003 Layout Page 2...

Страница 396: ...ADV8003 Hardware Manual Rev B August 2013 396 Figure 174 ADV8003 Layout Page 3...

Страница 397: ...ADV8003 Hardware Manual Rev B August 2013 397 Figure 175 ADV8003 Layout Page 4...

Страница 398: ...ADV8003 Hardware Manual Rev B August 2013 398 Figure 176 ADV8003 Layout Page 5...

Страница 399: ...ADV8003 Hardware Manual Rev B August 2013 399 Figure 177 ADV8003 Layout Page 6...

Страница 400: ...ADV8003 Hardware Manual Rev B August 2013 400 Figure 178 ADV8003 Layout Page 7...

Страница 401: ...ADV8003 Hardware Manual Rev B August 2013 401 Figure 179 ADV8003 Layout Page 8...

Страница 402: ...ADV8003 Hardware Manual Rev B August 2013 402 APPENDIX D PACKAGE OUTLINE DRAWING Refer to Section 1 4...

Страница 427: ...ADV8003 Hardware Manual Rev B August 2013 427 P 2 Z Z Z P 1 Z Z Z P 0 Z Z Z...