UG-549

ADuCM310 Hardware Reference Manual

Rev. C | Page 36 of 192

IDAC Thermal Shutdown

The

has an internal temperature sensor that monitors the die temperature. This temperature sensor can be monitored as an

ADC input channel; the measured voltage is proportional to die temperature. See the Temperature Sensor Settings section for more

information.

Internally, the die temperature is compared to a fixed voltage, proportional to approximately 130°C die temperature. If the die

temperature exceeds 130°C, there is a risk of damaging the die because the absolute maximum junction temperature rating is 150°C. As

the IDACs potentially consume the most power, the user may want to shut off the IDACs to reduce power and therefore reduce the die

temperature. Two options are available:

•

Enable a thermal interrupt by setting either INTSEL[12] or INTSEL[4]. If the die temperature exceeds the threshold of approximately

130°C, this interrupt is triggered and user code can take the appropriate action. This is the recommended procedure.

•

Another option is to enable automatic shutdown of the IDACs by setting the individual thermal shutdown bits for each IDAC via

IDACxCON[6]. If this bit is set in the appropriate IDACxCON register, the IDAC output current is reduced to 0 mA to reduce the

power consumption of the device and to reduce the die temperature of the device.

Note that the internal temperature sensor accuracy can be up to ±20°C and there is no way of calibrating the thermal shutdown trip point.

Therefore, it is recommended not to enable the automatic thermal shutdown feature (IDACxCON[6] = 0) without also enabling one of

the thermal interrupt sources (INTSEL[4] = 1 or INTSEL[12] = 1).

IDAC Reference Resistor Error Shutdown

The IREF pin is connected to ground via a 3.16 kΩ resistor to generate a reference current for the IDACs. The value of this resistor

directly affects the output current on the IDACs. If this resistor is less than 3.16 kΩ, the output current on all IDACs is higher than

expected; the output current scales with the resistor value.

The IDAC hardware has a fault detection circuit that detects if the IREF resistor is <50% of 3.16 kΩ (<1.58 kΩ). If the fault is detected on

the reference resistor, an interrupt can be generated.

•

If INTSEL[5] = 1, this fault detection circuit can generate an interrupt from the low voltage die and a status register is set to indicate

the fault.

•

While R

EXT

is detected as <1.58 kΩ, the IDAC outputs are automatically shut down (0 mA output) and remain off until R

EXT

rises

above the 1.58 kΩ threshold.

IDAC Output Filter

Each IDAC has a filter on the output stage to minimize noise. Each IDAC requires an external 10 nF capacitor between the PV

DD

supply

and its CDAMP pin (see the

data sheet). The on-chip, programmable resistor is controlled by the IDACxCON[5:2] bits.

Table 26 IDAC Filter Bandwidth Control Settings

IDACxCON[5:2]

R Value

Cutoff Frequency (f

C

)

0000

60 Ω

262 kHz

0101

5.6 kΩ

2.8 kHz

0110

11.2 kΩ

1.4 kHz

0111

22.2 kΩ

715 Hz

1000

44.4 kΩ

357 Hz

1001

104 kΩ

153 Hz

All other options are reserved

IDAC Data Register

The IDAC output is controlled by an internal 11-bit and 5-bit DAC.

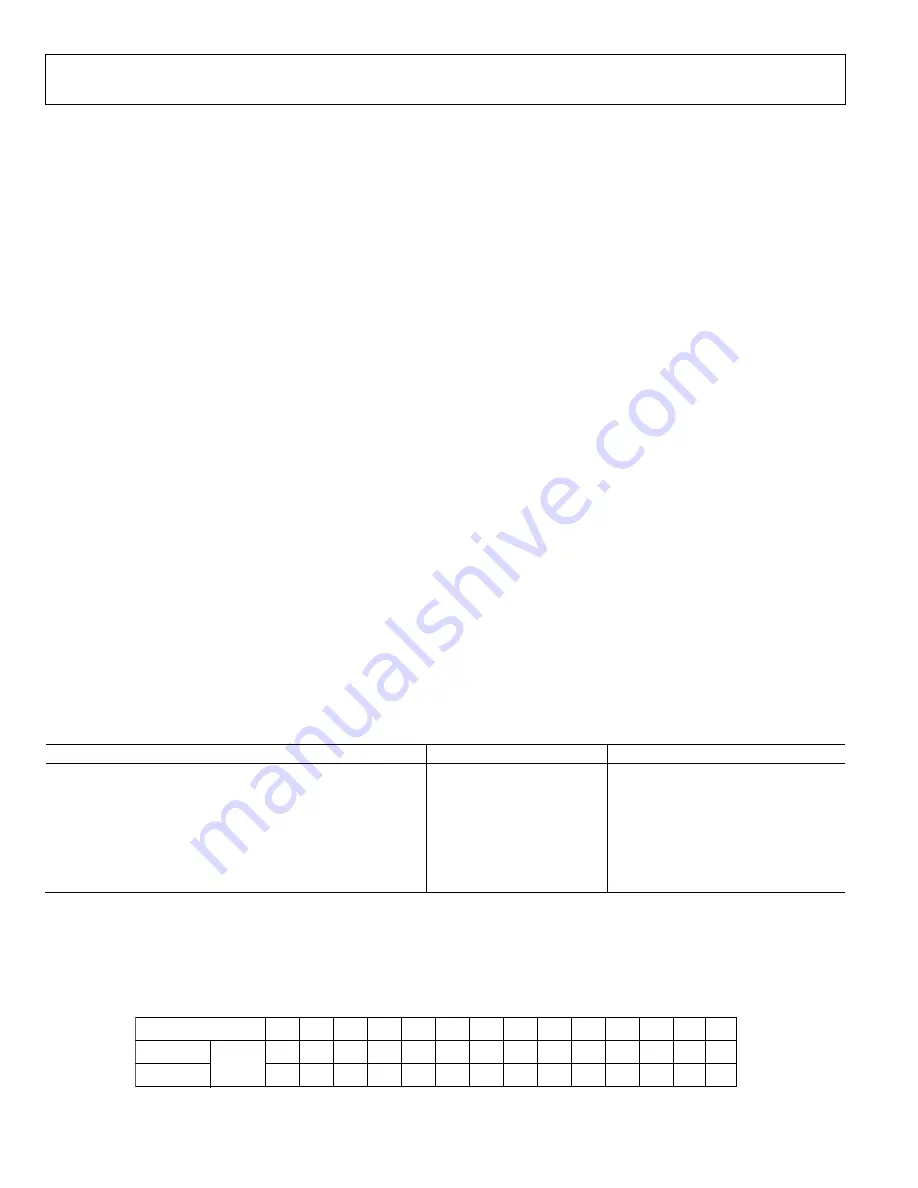

The 11-bit DAC (IDACxDAT[27:17]) controls the MSBs. The 5-bit DAC (IDACxDAT[16:12]) controls the LSBs. Bits[4:3] of the 5-bit

DAC overlap the high order 11-bit DAC. The two MSBs of the 5-bit DAC (IDACxDAT[16:15]) overlap the two LSBs of the 11-bit DAC

(IDACxDAT[18:17]), as shown in Figure 10.

13

12

11

10

9

8

7

6

5

4

3

2

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

1

0

12

IDACxDAT

14-BIT IDAC OUTPUT

11-BIT DAC

5-BIT DAC

1

1461-

010

Figure 10. 14-Bit IDAC Output