User Guide

UG-1283

Rev. A | Page 5 of 24

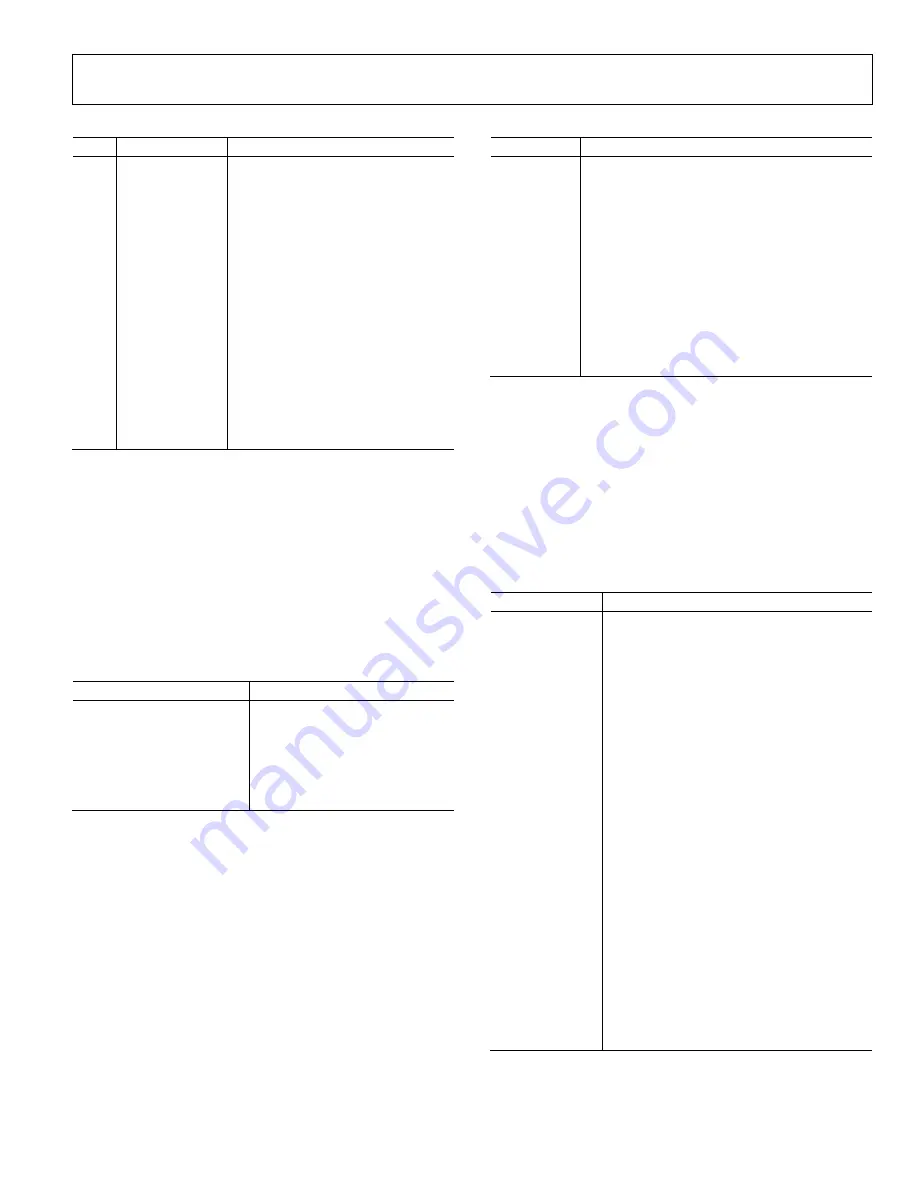

Table 4. 1.8 V Logic Connector P6 Pinout

Pin Signal

Name Function

1

CSB

Serial port enable input (active low)

2 AGND

Analog

ground

3 SDIO

Serial

data input and output

4 AGND

Analog

ground

5

SDO

Serial data output

6 AGND

Analog

ground

7

SCLK

Serial clock input

8 AGND

Analog

ground

9

TR

Transmit and receive switching input

10 AGND

Analog

ground

11

TX_LOAD

Load transmit configurations input

12 AGND

Analog

ground

13

RX_LOAD

Load receive configurations input

14 AGND

Analog

ground

15

PA_ON

PA bias enable input

16 AGND

Analog

ground

Board Address Selection

supports up to four devices on the same serial

peripheral interface (SPI) connection, with each device identified

by the corresponding ADDR0 and ADDR1 pin logic values and

addressed by the SPI bits (AD1 and AD0). See the

datasheet for more details. Jumper Block P10 allows the user to

determine whether the ADDR0 and ADDR1 pin values are high

or low, as shown in Table 5. Note that P10 is labeled AD0 and

AD1 on the ADAR1000-EVALZ, which corresponds to the

ADDR0 and ADDR1 pins, respectively.

Table 5. Jumper Block P10 Selections

Jumper Connection

Function

Position 1 to Position 3

AD1 is controlled by SDP GPIO2

Position 3 to Position 5

AD1 = high

Position 3 (Not Connected)

AD1 = low

Position 2 to Position 4

AD0 is controlled by SDP GPIO3

Position 4 to Position 6

AD0 = high

Position 4 (Not Connected)

AD0 = low

Peripheral Module-Compatible Interface

The 3.3 V digital interface signals are also repeated on

Connector P3, arranged to be compatible with the peripheral

module interface connector available on many field programmable

gate array (FPGA) evaluation kits or modules. Appropriate FPGA

programming is required to use this function. The pinout of the

P3 connector is shown in Table 6.

Table 6. Peripheral Module-Compatible Interface (P3)

Pin Signal

1 GPIO0

(RX_LOAD)

2 SPI_SEL_A

3 GPIO1

(TX_LOAD)

4 SPI_MOSI

5 GPIO4

(TR)

6 SPI_MISO

7 GPIO5

(PA_ON)

8 SPI_CLK

9 AGND

10 AGND

11 No

connect

12 No

connect

TRANSMIT AND RECEIVE MODULE CONTROL

SIGNALS

controls the operation of four transmit and

receive modules, which typically contain an LNA, a PA, a

transmit and receive selection switch, and possibly a polarization

selection switch. The 24-pin header, P9, contains signals in

groups of six to control the four transmit and receive modules.

The pinout of P9 is shown in Table 7.

Table 7. Transmit and Receive Module Interface

Connector P9 Pinout

Pin Signal

1 TR_SW_NEG

2 LNA_BIAS

3 TR_SW_POS

4 TR_POL

5 PA_BIAS4

6 AGND

7 TR_SW_NEG

8 LNA_BIAS

9 TR_SW_POS

10 TR_POL

11 PA_BIAS3

12 AGND

13 TR_SW_NEG

14 LNA_BIAS

15 TR_SW_POS

16 TR_POL

17 PA_BIAS2

18 AGND

19 TR_SW_NEG

20 LNA_BIAS

21 TR_SW_POS

22 TR_POL

23 PA_BIAS1

24 AGND