AD9956/PCB

Rev. 0 | Page 3 of 12

HARDWARE

SYSTEM REQUIREMENTS

To use the evaluation board and run the software, you need

the minimum system requirements listed in Table 1 on the

evaluation PC.

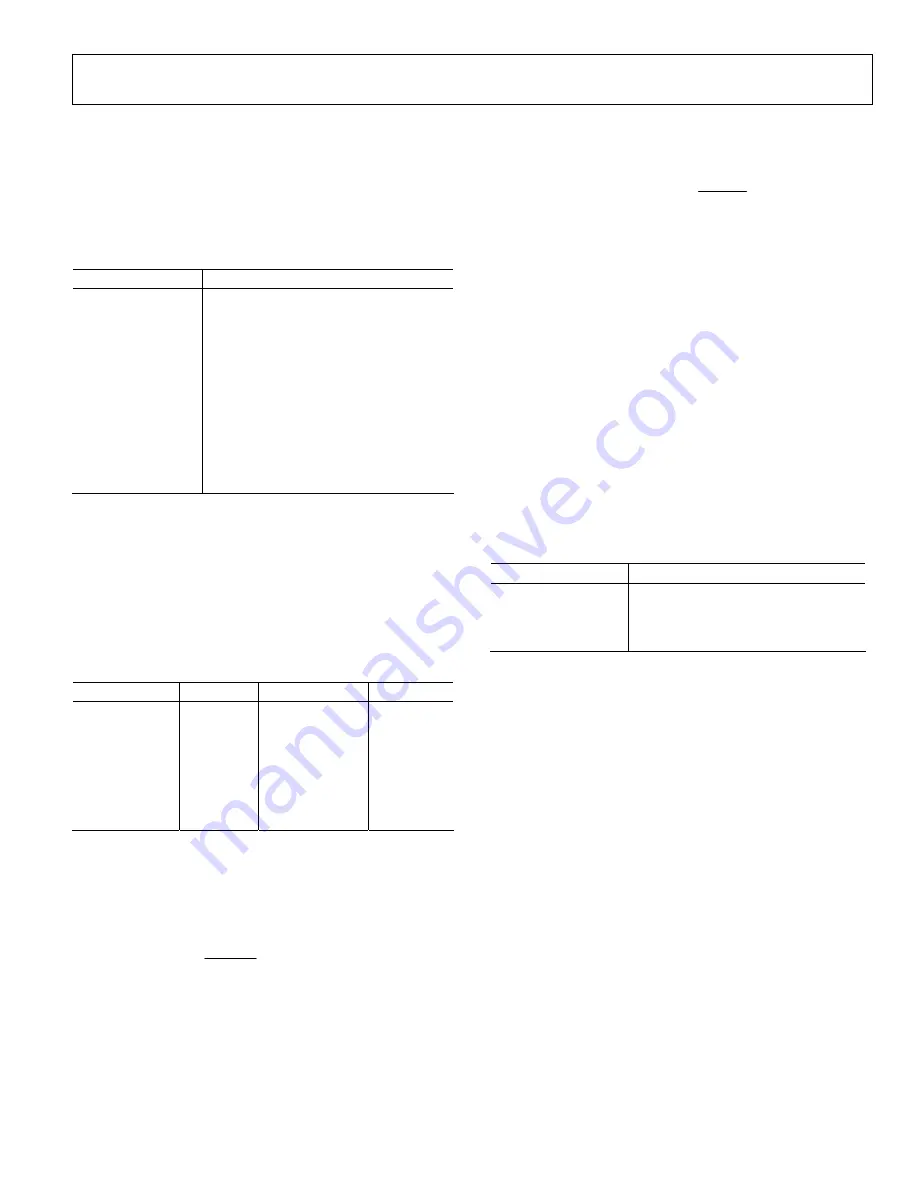

Table 1. System Requirements

Item Requirement

Operating System

Windows® 95 or greater

Processor

Pentium® I or better

Memory

128 MB or better

Ports

One USB port

Clocking

Signal generator capable of generating

sine waves of at least 3 dBm power, up to

at least 10 MHz

Power Supplies

Capability to generate at least 3 inde-

pendent dc voltages

Measurement

Appropriate measurement device, such

as a spectrum analyzer or a high

bandwidth oscilloscope

SETUP

Powering the Part

The AD9956/PCB evaluation board has three power supply

connectors: TB1, J14, and J17. TB1 powers the DDS, the phase

detector, and the PC interface logic. J14 powers the VCO (when

populated). J17 powers the CML output driver. Table 2 shows

the necessary connections and the appropriate biasing voltage.

Table 2. Connections and Biasing Voltage

Connector

Pin No.

Label

Voltage (V)

TB1 1

VCC 3.3

TB1 2

DVDD

1.8

TB1 3

GND 0

TB1 4

DVDD_I/O

3.3

TB1 5

AVDD

1.8

J14

VCO + 5 V

5

J17

AVDD_CP

3.3

Clocking the Part

The AD9956 can be configured in multiple ways to put the

device into a variety of different loops. The configuration deter-

mines the device input that serves as the input to the loop. To

clock the RF divider/DDS directly, connect the external clock-

ing signal to the DUT RF IN SMA connector, J1. This input

leads to the REFCLK/REFCLK inputs of the AD9956. In many

closed-loop applications, the VCO supplies this signal.

When using the part in this kind of application, the external

signal should be applied to the DUT REF IN connector, J2. This

leads to the AD9956 Pins PLLREF/PLLREF, the reference input

of the AD9956’s phase frequency detector. See the AD9956 data

sheet for details on the maximum input speeds and input

sensitivities of these two inputs.

Communicating with the Part

Two interface standards are available on the AD9956/PCB

evaluation board:

•

USB 2.0 interface

•

Header row (U9, U12), which places the part under the

control of an external controller (such as a µP, an FPGA,

or a DSP)

Analog Devices offers a GUI for the PC; it does not offer

control software for external controllers.

Use the jumper settings listed in Table 3 to enable different

modes of communication.

Table 3. Jumper Settings for Communication Modes

Mode Settings

PC control, USB port

Set W4 to PC. Place a jumper on W15.

External control

Set W3 to parallel, set W4 to manual,

and remove W15 (or leave it stored as a

shunt).

Master/Slave Configuration

To allow multiple devices to be driven by a common controller,

the evaluation hardware and software allow master/slave con-

figurations. When a board is configured as a master, it can be

connected directly to the USB port or the parallel port of a PC.

A slave can talk to the evaluation software only through another

AD9956 board, which acts as the master.

To configure two boards for this master/slave relationship,

connect a 26-wire ribbon cable from the master port (U9) of the

master board to the slave port (U12) of the slave board. On the

master board, set all the master/slave jumpers (W5 to W13) to

master. On the slave board, set W5 to W12 to slave. Once the

master/slave configuration is set, the evaluation software can

communicate with both because each of the dialog boxes has

an area for the master board and the slave board.

Содержание AD9953YSVZ

Страница 11: ...AD9956 PCB Rev 0 Page 11 of 12 NOTES...